Datasheet

Data Sheet AD9577

Rev. 0 | Page 37 of 44

MAX_BW

The normal bandwidth of PLL2 is 50 kHz. This low bandwidth

is required to filter the SDM phase noise. When SSCG is activated,

the bandwidth is increased to 125 kHz. There is a trade-off in

setting the PLL bandwidth between allowing the triangular-wave

modulation (that is, its higher order harmonics) to pass through

the PLL unattenuated and passing more SDM phase noise through

to the PLL output. Bringing the MAX_BW pin high changes the

PLL bandwidth to 250 kHz from its default value of 125 kHz

during SSCG operation. Increasing the PLL bandwidth results

in more SDM phase noise being passed unfiltered through to the

PLL output, but more of the triangular-wave harmonics are also

passed through, improving the triangular-wave accuracy.

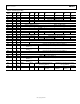

Table 29. Register Values for SSCG Example

Parameter Register Name Range Value (Decimal) Value(Binary)

NumSteps BS2[7:0], BS3[7] +1 to +511 +45 00101101

FracStep BS1[7:0] −128 to 0 −7 11111001

CkDiv BS3[6:0] +2 to +127 +9 0001001

FRAC BF0[7:0], BF1[7:4] 0 to +4094 +198 000011000110

MOD BF1[3:0], BF2[7:0] 0 to +4095 +625 001001110001

Nb BF3[5:0] 0 to +63 80 + 20 = 100 010100