Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- FUNCTIONAL BLOCK DIAGRAM

- PRODUCT HIGHLIGHTS

- TABLE OF CONTENTS

- REVISION HISTORY

- GENERAL DESCRIPTION

- SPECIFICATIONS

- ADC DC SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ80, AD9640ABCPZ-105, AND AD9640BCPZ-105

- ADC DC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ125, AD9640ABCPZ-150, AND AD9640BCPZ150

- ADC AC SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ80, AD9640ABCPZ-105, AND AD9640BCPZ-105

- ADC AC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ125, AD9640ABCPZ-150, AND AD9640BCPZ 150

- DIGITAL SPECIFICATIONS

- SWITCHING SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ-80, AD9640ABCPZ-105, AND AD9640BCPZ105

- SWITCHING SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ-125, AD9640ABCPZ-150, AND AD9640BCPZ150

- TIMING SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

- EQUIVALENT CIRCUITS

- TYPICAL PERFORMANCE CHARACTERISTICS

- THEORY OF OPERATION

- ADC OVERRANGE AND GAIN CONTROL

- SIGNAL MONITOR

- BUILT-IN SELF-TEST (BIST) AND OUTPUT TEST

- CHANNEL/CHIP SYNCHRONIZATION

- SERIAL PORT INTERFACE (SPI)

- MEMORY MAP

- READING THE MEMORY MAP TABLE

- EXTERNAL MEMORY MAP

- MEMORY MAP REGISTER DESCRIPTION

- Sync Control (Register 0x100)

- Fast Detect Control (Register 0x104)

- Fine Upper Threshold (Register 0x106 and Register 0x107)

- Fine Lower Threshold (Register 0x108 and Register 0x109)

- Signal Monitor DC Correction Control (Register 0x10C)

- Signal Monitor DC Value Channel A (Register 0x10D and Register 0x10E)

- Signal Monitor DC Value Channel B (Register 0x10F and Register 0x110)

- Signal Monitor SPORT Control (Register 0x111)

- Signal Monitor Control (Register 0x112)

- Signal Monitor Period (Register 0x113 to Register 0x115)

- Signal Monitor Result Channel A (Register 0x116 to Register 0x118)

- Signal Monitor Result Channel B (Register 0x119 to Register 0x11B)

- APPLICATIONS INFORMATION

- OUTLINE DIMENSIONS

AD9640

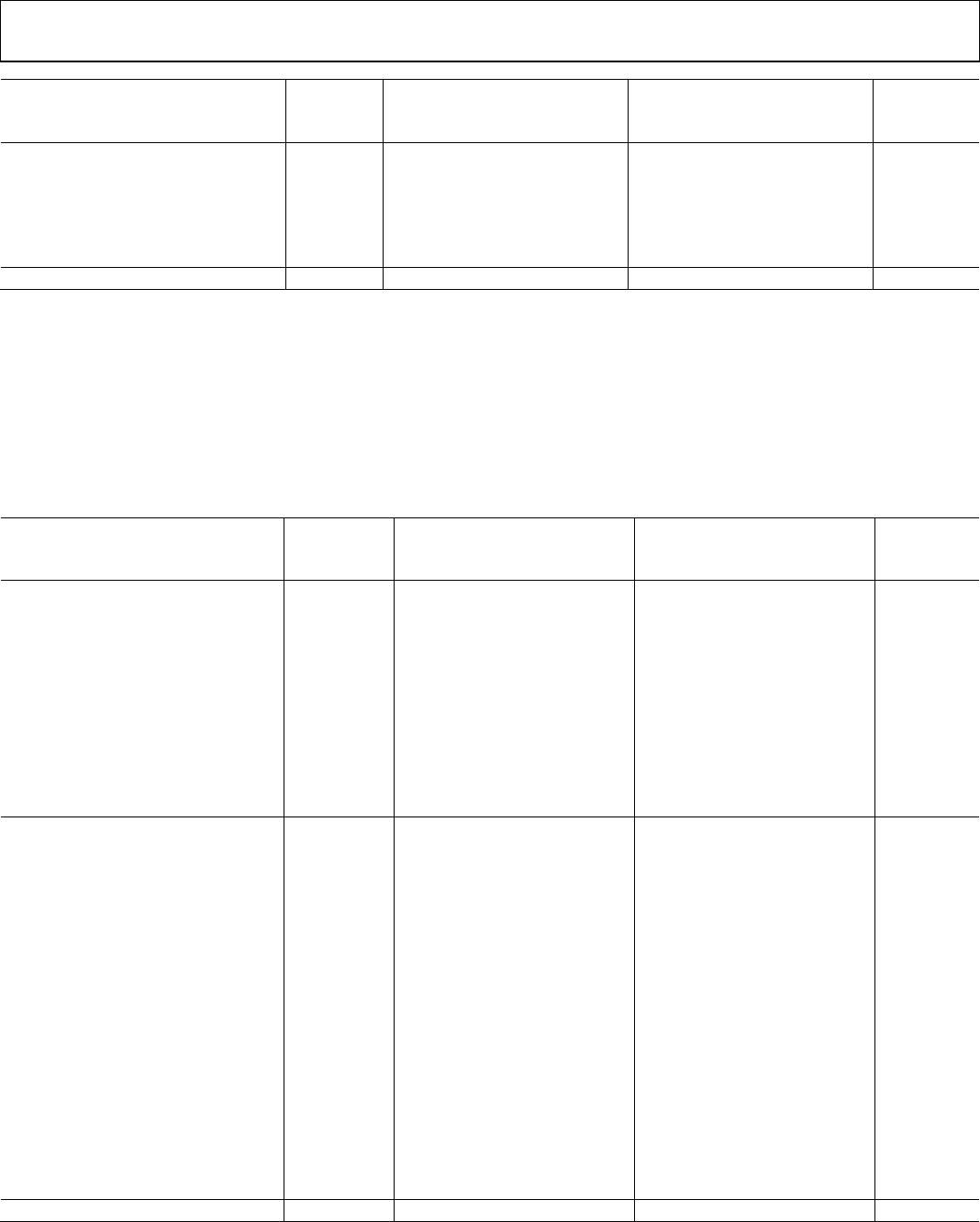

Rev. B | Page 11 of 52

Parameter Temp

AD9640ABCPZ-80

AD9640BCPZ-80

AD9640ABCPZ-105/

AD9640BCPZ-105

Unit

Min Typ Max Min Typ Max

CMOS Mode Pipeline Delay (Latency) Full 12 12 Cycles

LVDS Mode Pipeline Delay (Latency)

Channel A/Channel B

12/12.5 12/12.5 Cycles

Aperture Delay (t

A

) Full 1.0 1.0 ns

Aperture Uncertainty (Jitter, t

J

) Full 0.1 0.1 ps rms

Wake-Up Time

3

Full 350 350 μs

OUT-OF-RANGE RECOVERY TIME Full 2 2 Cycles

1

Conversion rate is the clock rate after the divider.

2

Output propagation delay is measured from CLK 50% transition to DATA 50% transition, with 5 pF load.

3

Wake-up time is dependent on the value of the decoupling capacitors.

SWITCHING SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ-125, AD9640ABCPZ-150, AND

AD9640BCPZ-150

AVDD = 1.8 V, DVDD = 1.8V, DRVDD = 3.3 V, maximum sample rate, VIN = −1.0 dBFS differential input, 1.0 V internal reference, DCS

enabled, unless otherwise noted.

Table 7.

Parameter Temperature

AD9640ABCPZ-125/

AD9640BCPZ-125

AD9640ABCPZ-150/

AD9640BCPZ-150

Unit

Min Typ Max Min Typ Max

CLOCK INPUT PARAMETERS

Input Clock Rate Full 625 625 MHz

Conversion Rate

DCS Enabled

1

Full 20 125 20 150 MSPS

DCS Disabled

1

Full 10 125 10 150 MSPS

CLK Period—Divide by 1 Mode (t

CLK

) Full 8 6.66 ns

CLK Pulse Width High

Divide by 1 Mode, DCS Enabled Full 2.4 4 5.6 2.0 3.33 4.66 ns

Divide by 1 Mode, DCS Disabled Full 3.6 4 4.4 3.0 3.33 3.66 ns

Divide by 2 Mode, DCS Enabled Full 1.6 1.6 ns

Divide by 3 Through 8, DCS Enabled Full 0.8 0.8 ns

DATA OUTPUT PARAMETERS (DATA, FD)

CMOS Mode—DRVDD = 3.3 V

Data Propagation Delay (t

PD

)

2

Full 2.2 4.5 6.4 2.2 4.5 6.4 ns

DCO Propagation Delay (t

DCO

) Full 3.8 5.0 6.8 3.8 5.0 6.8 ns

Setup Time (t

S

) Full 4.5 3.83 ns

Hold Time (t

H

) Full 3.5 2.83 ns

CMOS Mode—DRVDD = 1.8 V

Data Propagation Delay (t

PD

)

2

Full 2.4 5.2 6.9 2.4 5.2 6.9 ns

DCO Propagation Delay (t

DCO

) Full 4.0 5.6 7.3 4.0 5.6 7.3 ns

LVDS Mode—DRVDD = 1.8 V

Data Propagation Delay (t

PD

)

2

Full 3.0 3.8 4.5 3.0 3.8 4.5 ns

DCO Propagation Delay (t

DCO

) Full 5.0 6.2 7.4 4.8 5.9 7.3 ns

CMOS Mode Pipeline Delay (Latency) Full 12 12 Cycles

LVDS Mode Pipeline Delay (Latency)

Channel A/Channel B

12/12.5 12/12.5 Cycles

Aperture Delay (t

A

) Full 1.0 1.0 ns

Aperture Uncertainty (Jitter, t

J

) Full 0.1 0.1 ps rms

Wake-Up Time

3

Full 350 350 μs

OUT-OF-RANGE RECOVERY TIME Full 3 3 Cycles

1

Conversion rate is the clock rate after the divider.

2

Output propagation delay is measured from CLK 50% transition to DATA 50% transition, with 5 pF load.

3

Wake-up time is dependent on the value of the decoupling capacitors.