Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- FUNCTIONAL BLOCK DIAGRAM

- PRODUCT HIGHLIGHTS

- TABLE OF CONTENTS

- REVISION HISTORY

- GENERAL DESCRIPTION

- SPECIFICATIONS

- ADC DC SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ80, AD9640ABCPZ-105, AND AD9640BCPZ-105

- ADC DC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ125, AD9640ABCPZ-150, AND AD9640BCPZ150

- ADC AC SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ80, AD9640ABCPZ-105, AND AD9640BCPZ-105

- ADC AC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ125, AD9640ABCPZ-150, AND AD9640BCPZ 150

- DIGITAL SPECIFICATIONS

- SWITCHING SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ-80, AD9640ABCPZ-105, AND AD9640BCPZ105

- SWITCHING SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ-125, AD9640ABCPZ-150, AND AD9640BCPZ150

- TIMING SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

- EQUIVALENT CIRCUITS

- TYPICAL PERFORMANCE CHARACTERISTICS

- THEORY OF OPERATION

- ADC OVERRANGE AND GAIN CONTROL

- SIGNAL MONITOR

- BUILT-IN SELF-TEST (BIST) AND OUTPUT TEST

- CHANNEL/CHIP SYNCHRONIZATION

- SERIAL PORT INTERFACE (SPI)

- MEMORY MAP

- READING THE MEMORY MAP TABLE

- EXTERNAL MEMORY MAP

- MEMORY MAP REGISTER DESCRIPTION

- Sync Control (Register 0x100)

- Fast Detect Control (Register 0x104)

- Fine Upper Threshold (Register 0x106 and Register 0x107)

- Fine Lower Threshold (Register 0x108 and Register 0x109)

- Signal Monitor DC Correction Control (Register 0x10C)

- Signal Monitor DC Value Channel A (Register 0x10D and Register 0x10E)

- Signal Monitor DC Value Channel B (Register 0x10F and Register 0x110)

- Signal Monitor SPORT Control (Register 0x111)

- Signal Monitor Control (Register 0x112)

- Signal Monitor Period (Register 0x113 to Register 0x115)

- Signal Monitor Result Channel A (Register 0x116 to Register 0x118)

- Signal Monitor Result Channel B (Register 0x119 to Register 0x11B)

- APPLICATIONS INFORMATION

- OUTLINE DIMENSIONS

AD9640

Rev. B | Page 16 of 52

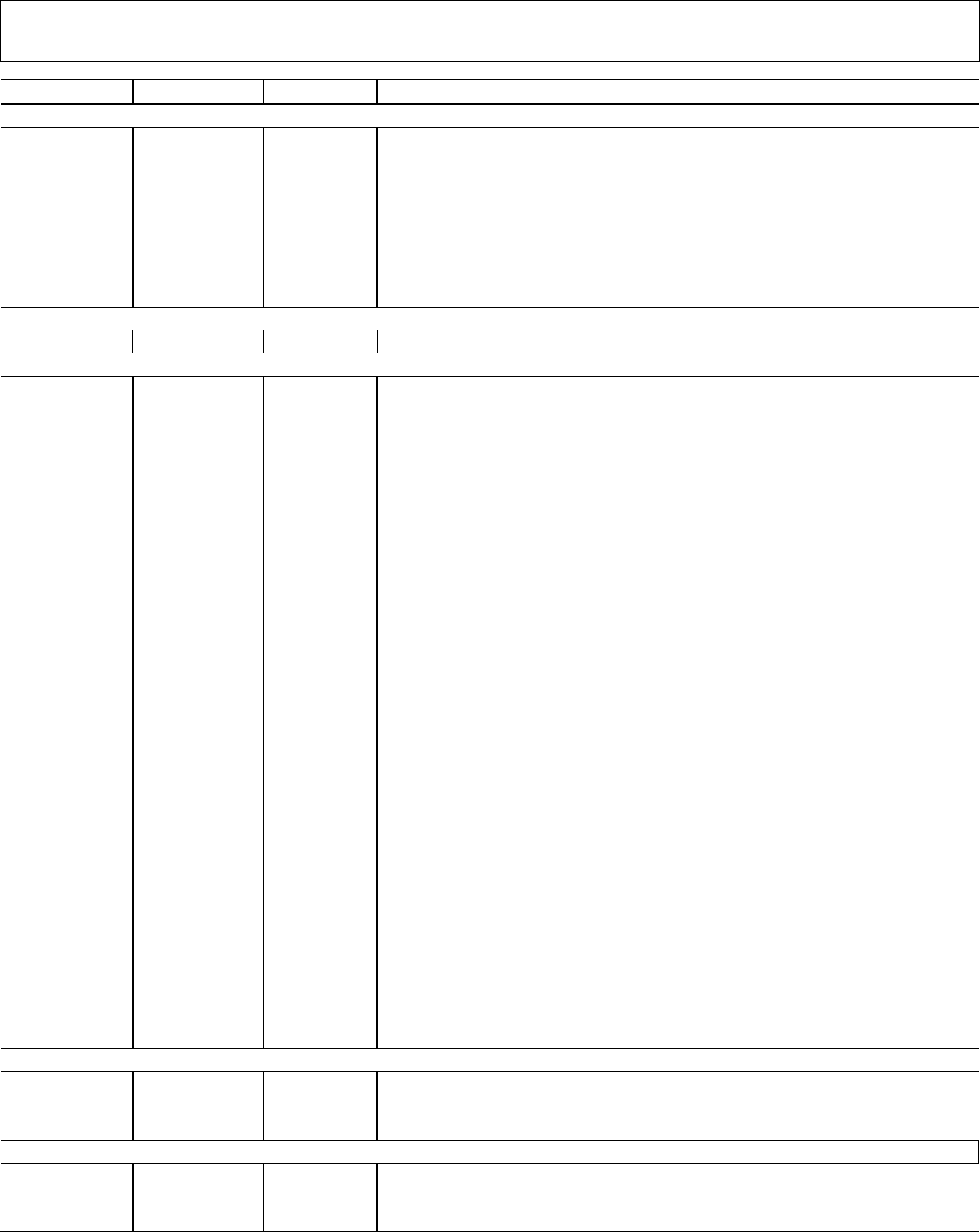

Pin No. Mnemonic Type Description

ADC Fast Detect Outputs

29 FD0A Output Channel A Fast Detect Indicator. See Table 18 for details.

30 FD1A Output Channel A Fast Detect Indicator. See Table 18 for details.

31 FD2A Output Channel A Fast Detect Indicator. See Table 18 for details.

32 FD3A Output Channel A Fast Detect Indicator. See Table 18 for details.

53 FD0B Output Channel B Fast Detect Indicator. See Table 18 for details.

54 FD1B Output Channel B Fast Detect Indicator. See Table 18 for details.

55 FD2B Output Channel B Fast Detect Indicator. See Table 18 for details.

56 FD3B Output Channel B Fast Detect Indicator. See Table 18 for details.

Digital Inputs

52 SYNC Input Digital Synchronization Pin. Slave mode only.

Digital Outputs

12 D0A (LSB) Output Channel A CMOS Output Data.

13 D1A Output Channel A CMOS Output Data.

14 D2A Output Channel A CMOS Output Data.

15 D3A Output Channel A CMOS Output Data.

16 D4A Output Channel A CMOS Output Data.

17 D5A Output Channel A CMOS Output Data.

18 D6A Output Channel A CMOS Output Data.

19 D7A Output Channel A CMOS Output Data.

22 D8A Output Channel A CMOS Output Data.

23 D9A Output Channel A CMOS Output Data.

25 D10A Output Channel A CMOS Output Data.

26 D11A Output Channel A CMOS Output Data.

27 D12A Output Channel A CMOS Output Data.

28 D13A (MSB) Output Channel A CMOS Output Data.

58 D0B (LSB) Output Channel B CMOS Output Data.

59 D1B Output Channel B CMOS Output Data.

60 D2B Output Channel B CMOS Output Data.

61 D3B Output Channel B CMOS Output Data.

62 D4B Output Channel B CMOS Output Data.

63 D5B Output Channel B CMOS Output Data.

2 D6B Output Channel B CMOS Output Data.

3 D7B Output Channel B CMOS Output Data.

4 D8B Output Channel B CMOS Output Data.

5 D9B Output Channel B CMOS Output Data.

6 D10B Output Channel B CMOS Output Data.

7 D11B Output Channel B CMOS Output Data.

8 D12B Output Channel B CMOS Output Data.

9 D13B (MSB) Output Channel B CMOS Output Data.

11 DCOA Output Channel A Data Clock Output.

10 DCOB Output Channel B Data Clock Output.

SPI Control

48 SCLK/DFS Input SPI Serial Clock/Data Format Select Pin in External Pin Mode.

47 SDIO/DCS Input/Output SPI Serial Data I/O/Duty Cycle Stabilizer in External Pin Mode.

51 CSB Input SPI Chip Select (Active Low).

Serial Port

33 SMI SDO/OEB Input/Output Signal Monitor Serial Data Output/Output Enable Input (Active Low) in External Pin Mode.

35 SMI SDFS Output Signal Monitor Serial Data Frame Sync.

34 SMI SCLK/PDWN Input/Output Signal Monitor Serial Clock Output/Power-Down Input in External Pin Mode.