Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- FUNCTIONAL BLOCK DIAGRAM

- PRODUCT HIGHLIGHTS

- TABLE OF CONTENTS

- REVISION HISTORY

- GENERAL DESCRIPTION

- SPECIFICATIONS

- ADC DC SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ80, AD9640ABCPZ-105, AND AD9640BCPZ-105

- ADC DC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ125, AD9640ABCPZ-150, AND AD9640BCPZ150

- ADC AC SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ80, AD9640ABCPZ-105, AND AD9640BCPZ-105

- ADC AC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ125, AD9640ABCPZ-150, AND AD9640BCPZ 150

- DIGITAL SPECIFICATIONS

- SWITCHING SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ-80, AD9640ABCPZ-105, AND AD9640BCPZ105

- SWITCHING SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ-125, AD9640ABCPZ-150, AND AD9640BCPZ150

- TIMING SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

- EQUIVALENT CIRCUITS

- TYPICAL PERFORMANCE CHARACTERISTICS

- THEORY OF OPERATION

- ADC OVERRANGE AND GAIN CONTROL

- SIGNAL MONITOR

- BUILT-IN SELF-TEST (BIST) AND OUTPUT TEST

- CHANNEL/CHIP SYNCHRONIZATION

- SERIAL PORT INTERFACE (SPI)

- MEMORY MAP

- READING THE MEMORY MAP TABLE

- EXTERNAL MEMORY MAP

- MEMORY MAP REGISTER DESCRIPTION

- Sync Control (Register 0x100)

- Fast Detect Control (Register 0x104)

- Fine Upper Threshold (Register 0x106 and Register 0x107)

- Fine Lower Threshold (Register 0x108 and Register 0x109)

- Signal Monitor DC Correction Control (Register 0x10C)

- Signal Monitor DC Value Channel A (Register 0x10D and Register 0x10E)

- Signal Monitor DC Value Channel B (Register 0x10F and Register 0x110)

- Signal Monitor SPORT Control (Register 0x111)

- Signal Monitor Control (Register 0x112)

- Signal Monitor Period (Register 0x113 to Register 0x115)

- Signal Monitor Result Channel A (Register 0x116 to Register 0x118)

- Signal Monitor Result Channel B (Register 0x119 to Register 0x11B)

- APPLICATIONS INFORMATION

- OUTLINE DIMENSIONS

AD9640

Rev. B | Page 32 of 52

ADC OVERRANGE AND GAIN CONTROL

In receiver applications, it is desirable to have a mechanism to

reliably determine when the converter is about to be clipped.

The standard overflow indicator provides after-the-fact infor-

mation on the state of the analog input that is of limited usefulness.

Therefore, it is helpful to have a programmable threshold below

full scale that allows time to reduce the gain before the clip

actually occurs. In addition, because input signals can have

significant slew rates, latency of this function is of major concern.

Highly pipelined converters can have significant latency. A good

compromise is to use the output bits from the first stage of the

ADC for this function. Latency for these output bits is very low,

and overall resolution is not highly significant. Peak input signals

are typically between full scale and 6 dB to 10 dB below full

scale. A 3-bit or 4-bit output provides adequate range and

resolution for this function.

Using the SPI port, the user can provide a threshold above which

an overrange output is active. As long as the signal is below that

threshold, the output should remain low. The fast detect outputs

can also be programmed via the SPI port so that one of the pins

functions as a traditional overrange pin for customers who

currently use this feature. In this mode, all 14 bits of the converter

are examined in the traditional manner, and the output is high for

the condition normally defined as overflow. In either mode, the

magnitude of the data is considered in the calculation of the

condition (but the sign of the data is not considered). The threshold

detection responds identically to positive and negative signals

outside the desired range (magnitude).

FAST DETECT OVERVIEW

The AD9640 contains circuitry to facilitate fast overrange detec-

tion, allowing very flexible external gain control implementations.

Each ADC has four fast detect (FD) output pins that are used

to output information about the current state of the ADC input

level. The function of these pins is programmable via the fast detect

mode select bits and the fast detect enable bit in Register 0x104,

allowing range information to be output from several points in

the internal datapath. These output pins can also be set up to

indicate the presence of overrange or underrange conditions,

according to programmable threshold levels. Table 17 shows the

six configurations available for the fast detect pins.

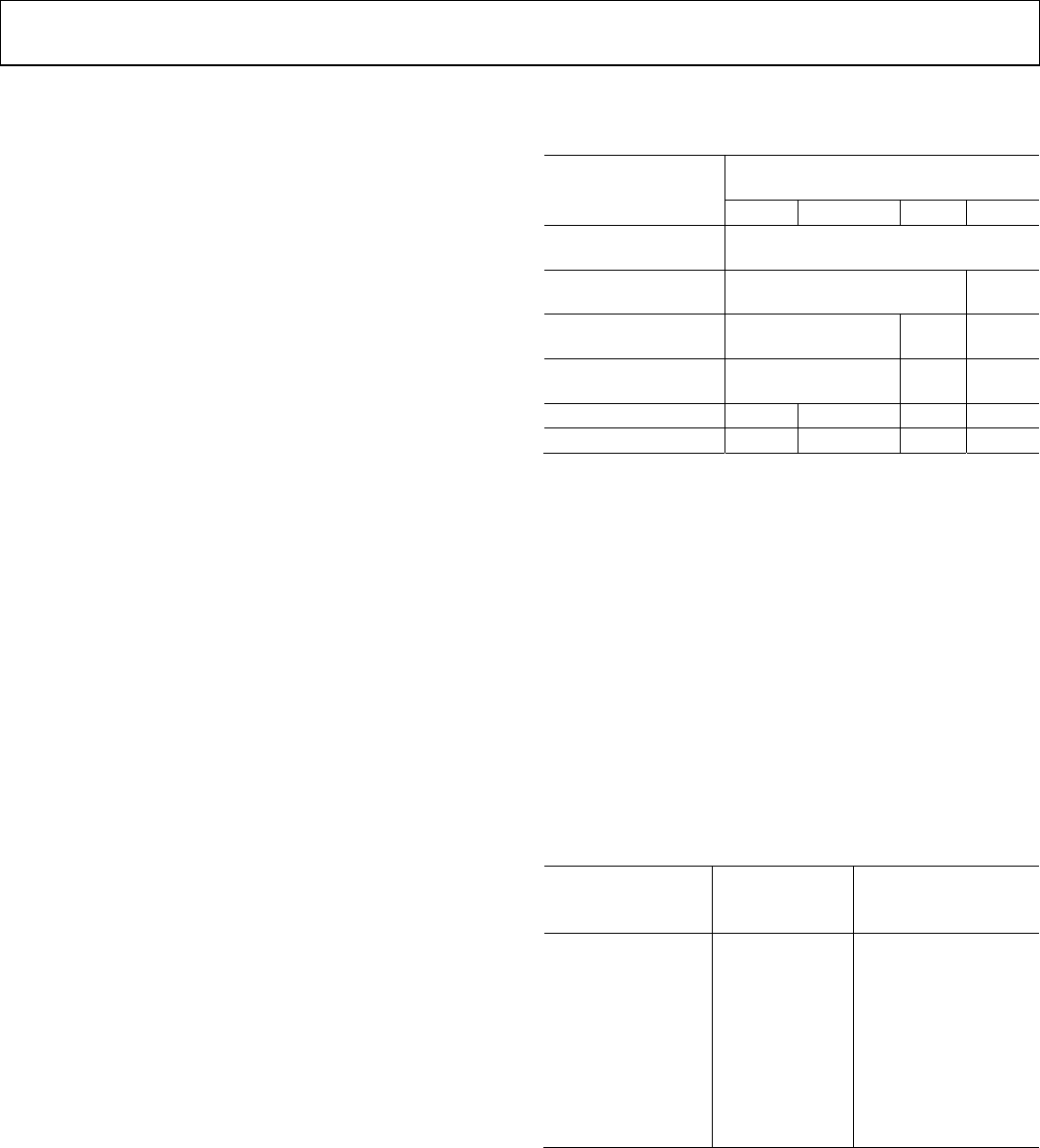

Table 17. Fast Detect Mode Select Bits Settings

Fast Detect

Mode Select Bits

(Register 0x104[3:1])

Information Presented on

Fast Detect (FD) Pins of Each ADC

1, 2

FD3 FD2 FD1 FD0

000

ADC fast magnitude

(see Table 18)

001

ADC fast magnitude

(see Table 19)

OR

010

ADC fast magnitude

(see Table 20)

OR F_LT

011

ADC fast magnitude

(see Table 20)

C_UT F_LT

100 OR C_UT F_UT F_LT

101 OR F_UT IG DG

1

The fast detect pins are FD0A/FD0B to FD3A/FD3B for the CMOS mode

configuration and FD0+/FD0− to FD3+/FD3− for the LVDS mode configuration.

2

See the ADC Overrange (OR) and Gain Switching sections for more

information about OR, C_UT, F_UT, F_LT, IG, and DG.

ADC FAST MAGNITUDE

When the fast detect output pins are configured to output the ADC

fast magnitude (that is, when the fast detect mode select bits are

set to 0b000), the information presented is the ADC level from

an early converter stage with a latency of only two clock cycles

(when in CMOS output mode). Using the fast detect output pins

in this configuration provides the earliest possible level indication

information. Because this information is provided early in the

datapath, there is significant uncertainty in the level indicated.

The nominal levels, along with the uncertainty indicated by the

ADC fast magnitude, are shown in Table 18.

Table 18. ADC Fast Magnitude Nominal Levels with Fast Detect

Mode Select Bits = 000

ADC Fast

Magnitude on

FD[3:0] Pins

Nominal Input

Magnitude

Below FS (dB)

Nominal Input

Magnitude

Uncertainty (dB)

0000 <−24 Minimum to −18.07

0001 −24 to −14.5 −30.14 to −12.04

0010 −14.5 to −10 −18.07 to −8.52

0011 −10 to −7 −12.04 to −6.02

0100 −7 to −5 −8.52 to −4.08

0101 −5 to −3.25 −6.02 to −2.5

0110 −3.25 to −1.8 −4.08 to −1.16

0111 −1.8 to −0.56 −2.5 to FS

1000 −0.56 to 0 −1.16 to 0