Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- FUNCTIONAL BLOCK DIAGRAM

- PRODUCT HIGHLIGHTS

- TABLE OF CONTENTS

- REVISION HISTORY

- GENERAL DESCRIPTION

- SPECIFICATIONS

- ADC DC SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ80, AD9640ABCPZ-105, AND AD9640BCPZ-105

- ADC DC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ125, AD9640ABCPZ-150, AND AD9640BCPZ150

- ADC AC SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ80, AD9640ABCPZ-105, AND AD9640BCPZ-105

- ADC AC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ125, AD9640ABCPZ-150, AND AD9640BCPZ 150

- DIGITAL SPECIFICATIONS

- SWITCHING SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ-80, AD9640ABCPZ-105, AND AD9640BCPZ105

- SWITCHING SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ-125, AD9640ABCPZ-150, AND AD9640BCPZ150

- TIMING SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

- EQUIVALENT CIRCUITS

- TYPICAL PERFORMANCE CHARACTERISTICS

- THEORY OF OPERATION

- ADC OVERRANGE AND GAIN CONTROL

- SIGNAL MONITOR

- BUILT-IN SELF-TEST (BIST) AND OUTPUT TEST

- CHANNEL/CHIP SYNCHRONIZATION

- SERIAL PORT INTERFACE (SPI)

- MEMORY MAP

- READING THE MEMORY MAP TABLE

- EXTERNAL MEMORY MAP

- MEMORY MAP REGISTER DESCRIPTION

- Sync Control (Register 0x100)

- Fast Detect Control (Register 0x104)

- Fine Upper Threshold (Register 0x106 and Register 0x107)

- Fine Lower Threshold (Register 0x108 and Register 0x109)

- Signal Monitor DC Correction Control (Register 0x10C)

- Signal Monitor DC Value Channel A (Register 0x10D and Register 0x10E)

- Signal Monitor DC Value Channel B (Register 0x10F and Register 0x110)

- Signal Monitor SPORT Control (Register 0x111)

- Signal Monitor Control (Register 0x112)

- Signal Monitor Period (Register 0x113 to Register 0x115)

- Signal Monitor Result Channel A (Register 0x116 to Register 0x118)

- Signal Monitor Result Channel B (Register 0x119 to Register 0x11B)

- APPLICATIONS INFORMATION

- OUTLINE DIMENSIONS

AD9640

Rev. B | Page 46 of 52

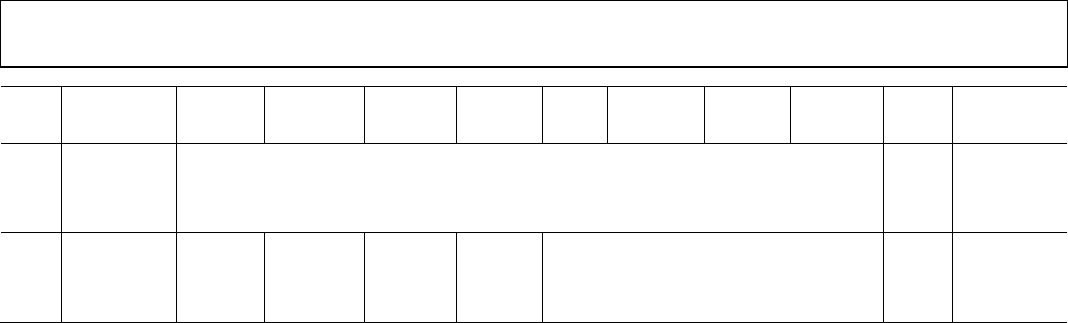

Addr

(Hex)

Register

Name

Bit 7

(MSB)

Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1

Bit 0

(LSB)

Default

Value

(Hex)

Default

Notes/

Comments

0x11A

Signal Monitor

Result

Channel B

Register 1

(Global)

Signal Monitor Result Channel B[15:8] Read only

0x11B

Signal Monitor

Result

Channel B

Register 2

(Global)

Open Open Open Open Signal Monitor Result Channel B[19:16] Read only

MEMORY MAP REGISTER DESCRIPTION

For additional information about functions controlled in

Register 0x00 to Register 0xFF, see the AN-877 Application Note,

Interfacing to High Speed ADCs via SPI.

Sync Control (Register 0x100)

Bit 7—Signal Monitor Sync Enable

Bit 7 enables the sync pulse from the external SYNC input to

the signal monitor block. The sync signal is passed when Bit 7

is high and Bit 0 is high. This is continuous sync mode.

Bits[6:3]—Reserved

Bit 2—Clock Divider Next Sync Only

If the sync enable bit (Address 0x100[0]) is high and the clock

divider sync enable (Address 0x100[1]) is high, Bit 2 allows the

clock divider to sync to the first sync pulse it receives and ignore

the rest. Address 0x100[1] resets after it syncs.

Bit 1—Clock Divider Sync Enable

Bit 1 gates the sync pulse to the clock divider. The sync signal is

passed when Bit 1 is high and Bit 0 is high. This is continuous

sync mode.

Bit 0—Master Sync Enable

Bit 0 must be high to enable any of the sync functions.

Fast Detect Control (Register 0x104)

Bits[7:4]—Reserved

Bits[3:1]—Fast Detect Mode Select

These bits set the mode of the fast detect output bits according

to Table 17.

Bit 0—Fast Detect Enable

Bit 0 is used to enable the fast detect bits. When the fast detect

outputs are disabled, the outputs go into a high impedance state.

In LVDS mode, when the outputs are interleaved, the outputs go

high-Z only if both channels are turned off (power-down/standby/

output disabled). If only one channel is turned off (power-down/

standby/output disabled), the fast detect outputs repeat the data

of the active channel.

Fine Upper Threshold (Register 0x106 and Register 0x107)

Register 0x106, Bits[7:0]—Fine Upper Threshold[7:0]

Register 0x107, Bits[7:5]—Reserved

Register 0x107, Bits[4:0]—Fine Upper Threshold[12:8]

These registers provide the fine upper limit threshold. This 13-bit

value is compared to the 13-bit magnitude from the ADC block

and, if the ADC magnitude exceeds this threshold value, the

F_UT flag is set.

Fine Lower Threshold (Register 0x108 and Register 0x109)

Register 0x108, Bits[7:0]—Fine Lower Threshold[7:0]

Register 0x109, Bits[7:5]—Reserved

Register 0x109, Bits[4:0]—Fine Lower Threshold[12:8]

These registers provide a fine lower limit threshold. This 13-bit

value is compared to the 13-bit magnitude from the ADC block

and, if the ADC magnitude is less than this threshold value, the

F_LT flag is set.

Signal Monitor DC Correction Control (Register 0x10C)

Bit 7—Reserved

Bit 6—DC Correction Freeze

When Bit 6 is set high, the dc correction is no longer updated

to the signal monitoring block. It holds the last dc value it

calculated.

Bits[5:2]—DC Correction Bandwidth

These bits set the averaging time of the signal monitor dc correc-

tion function. It is a 4-bit word that sets the bandwidth of the

correction block (see Table 26).