Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- FUNCTIONAL BLOCK DIAGRAM

- PRODUCT HIGHLIGHTS

- TABLE OF CONTENTS

- REVISION HISTORY

- GENERAL DESCRIPTION

- SPECIFICATIONS

- ADC DC SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ80, AD9640ABCPZ-105, AND AD9640BCPZ-105

- ADC DC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ125, AD9640ABCPZ-150, AND AD9640BCPZ150

- ADC AC SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ80, AD9640ABCPZ-105, AND AD9640BCPZ-105

- ADC AC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ125, AD9640ABCPZ-150, AND AD9640BCPZ 150

- DIGITAL SPECIFICATIONS

- SWITCHING SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ-80, AD9640ABCPZ-105, AND AD9640BCPZ105

- SWITCHING SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ-125, AD9640ABCPZ-150, AND AD9640BCPZ150

- TIMING SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

- EQUIVALENT CIRCUITS

- TYPICAL PERFORMANCE CHARACTERISTICS

- THEORY OF OPERATION

- ADC OVERRANGE AND GAIN CONTROL

- SIGNAL MONITOR

- BUILT-IN SELF-TEST (BIST) AND OUTPUT TEST

- CHANNEL/CHIP SYNCHRONIZATION

- SERIAL PORT INTERFACE (SPI)

- MEMORY MAP

- READING THE MEMORY MAP TABLE

- EXTERNAL MEMORY MAP

- MEMORY MAP REGISTER DESCRIPTION

- Sync Control (Register 0x100)

- Fast Detect Control (Register 0x104)

- Fine Upper Threshold (Register 0x106 and Register 0x107)

- Fine Lower Threshold (Register 0x108 and Register 0x109)

- Signal Monitor DC Correction Control (Register 0x10C)

- Signal Monitor DC Value Channel A (Register 0x10D and Register 0x10E)

- Signal Monitor DC Value Channel B (Register 0x10F and Register 0x110)

- Signal Monitor SPORT Control (Register 0x111)

- Signal Monitor Control (Register 0x112)

- Signal Monitor Period (Register 0x113 to Register 0x115)

- Signal Monitor Result Channel A (Register 0x116 to Register 0x118)

- Signal Monitor Result Channel B (Register 0x119 to Register 0x11B)

- APPLICATIONS INFORMATION

- OUTLINE DIMENSIONS

AD9640

Rev. B | Page 50 of 52

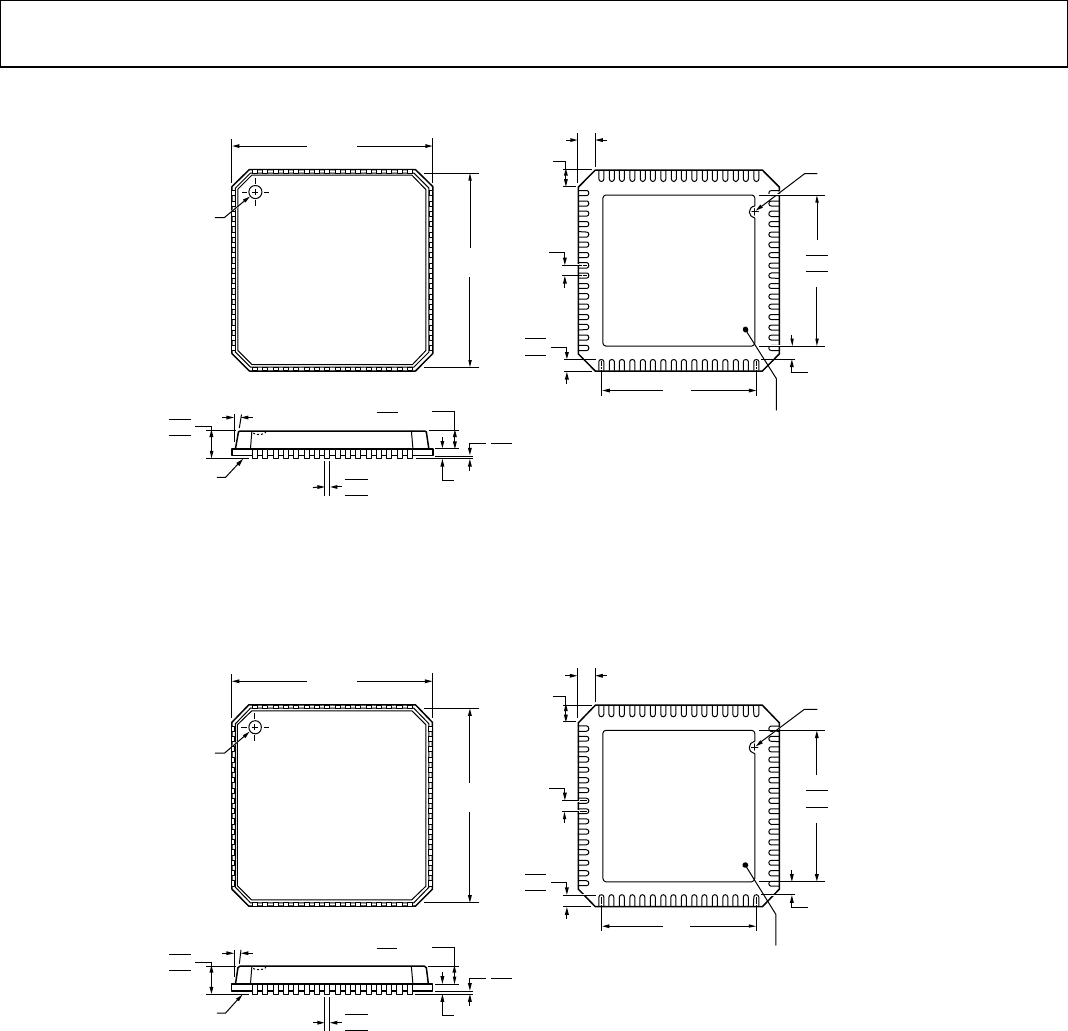

OUTLINE DIMENSIONS

COMPLIANT TO JEDEC STANDARDS MO-220-VMMD-4

080108-C

0.25 MIN

TOP VIEW

8.75

BSC SQ

9.00

BSC SQ

1

64

16

17

49

48

32

33

0.50

0.40

0.30

0.50

BSC

0.20 REF

12° MAX

0.80 MAX

0.65 TYP

1.00

0.85

0.80

7.50

REF

0.05 MAX

0.02 NOM

0.60 MAX

0.60

MAX

EXPOSED PAD

(BOTTOM VIEW)

SEATING

PLANE

PIN 1

INDICATOR

7.25

7.10 SQ

6.95

PIN 1

INDICATOR

0.30

0.23

0.18

FOR PROPER CONNECTION OF

THE EXPOSED PAD, REFER TO

THE PIN CONFIGURATION AND

FUNCTION DESCRIPTIONS

SECTION OF THIS DATA SHEET.

Figure 74. 64-Lead Lead Frame Chip Scale Package [LFCSP_VQ]

9 mm × 9 mm Body, Very Thin Quad

(CP-64-3)

Dimensions shown in millimeters

COMPLIANT TO JEDEC STANDARDS MO-220-VMMD-4

041509-A

0.25 MIN

TOP VIEW

8.75

BSC SQ

9.00

BSC SQ

1

64

16

17

49

48

32

33

0.50

0.40

0.30

0.50

BSC

0.20 REF

12° MAX

0.80 MAX

0.65 TYP

1.00

0.85

0.80

7.50

REF

0.05 MAX

0.02 NOM

0.60 MAX

0.60

MAX

EXPOSED PAD

(BOTTOM VIEW)

SEATING

PLANE

PIN 1

INDICATOR

7.65

7.50 SQ

7.35

PIN 1

INDICATOR

0.30

0.23

0.18

FOR PROPER CONNECTION OF

THE EXPOSED PAD, REFER TO

THE PIN CONFIGURATION AND

FUNCTION DESCRIPTIONS

SECTION OF THIS DATA SHEET.

Figure 75. 64-Lead Lead Frame Chip Scale Package [LFCSP_VQ]

9 mm × 9 mm Body, Very Thin Quad

(CP-64-6)

Dimensions shown in millimeters