Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- FUNCTIONAL BLOCK DIAGRAM

- PRODUCT HIGHLIGHTS

- TABLE OF CONTENTS

- REVISION HISTORY

- GENERAL DESCRIPTION

- SPECIFICATIONS

- ADC DC SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ80, AD9640ABCPZ-105, AND AD9640BCPZ-105

- ADC DC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ125, AD9640ABCPZ-150, AND AD9640BCPZ150

- ADC AC SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ80, AD9640ABCPZ-105, AND AD9640BCPZ-105

- ADC AC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ125, AD9640ABCPZ-150, AND AD9640BCPZ 150

- DIGITAL SPECIFICATIONS

- SWITCHING SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ-80, AD9640ABCPZ-105, AND AD9640BCPZ105

- SWITCHING SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ-125, AD9640ABCPZ-150, AND AD9640BCPZ150

- TIMING SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

- EQUIVALENT CIRCUITS

- TYPICAL PERFORMANCE CHARACTERISTICS

- THEORY OF OPERATION

- ADC OVERRANGE AND GAIN CONTROL

- SIGNAL MONITOR

- BUILT-IN SELF-TEST (BIST) AND OUTPUT TEST

- CHANNEL/CHIP SYNCHRONIZATION

- SERIAL PORT INTERFACE (SPI)

- MEMORY MAP

- READING THE MEMORY MAP TABLE

- EXTERNAL MEMORY MAP

- MEMORY MAP REGISTER DESCRIPTION

- Sync Control (Register 0x100)

- Fast Detect Control (Register 0x104)

- Fine Upper Threshold (Register 0x106 and Register 0x107)

- Fine Lower Threshold (Register 0x108 and Register 0x109)

- Signal Monitor DC Correction Control (Register 0x10C)

- Signal Monitor DC Value Channel A (Register 0x10D and Register 0x10E)

- Signal Monitor DC Value Channel B (Register 0x10F and Register 0x110)

- Signal Monitor SPORT Control (Register 0x111)

- Signal Monitor Control (Register 0x112)

- Signal Monitor Period (Register 0x113 to Register 0x115)

- Signal Monitor Result Channel A (Register 0x116 to Register 0x118)

- Signal Monitor Result Channel B (Register 0x119 to Register 0x11B)

- APPLICATIONS INFORMATION

- OUTLINE DIMENSIONS

AD9640

Rev. B | Page 6 of 52

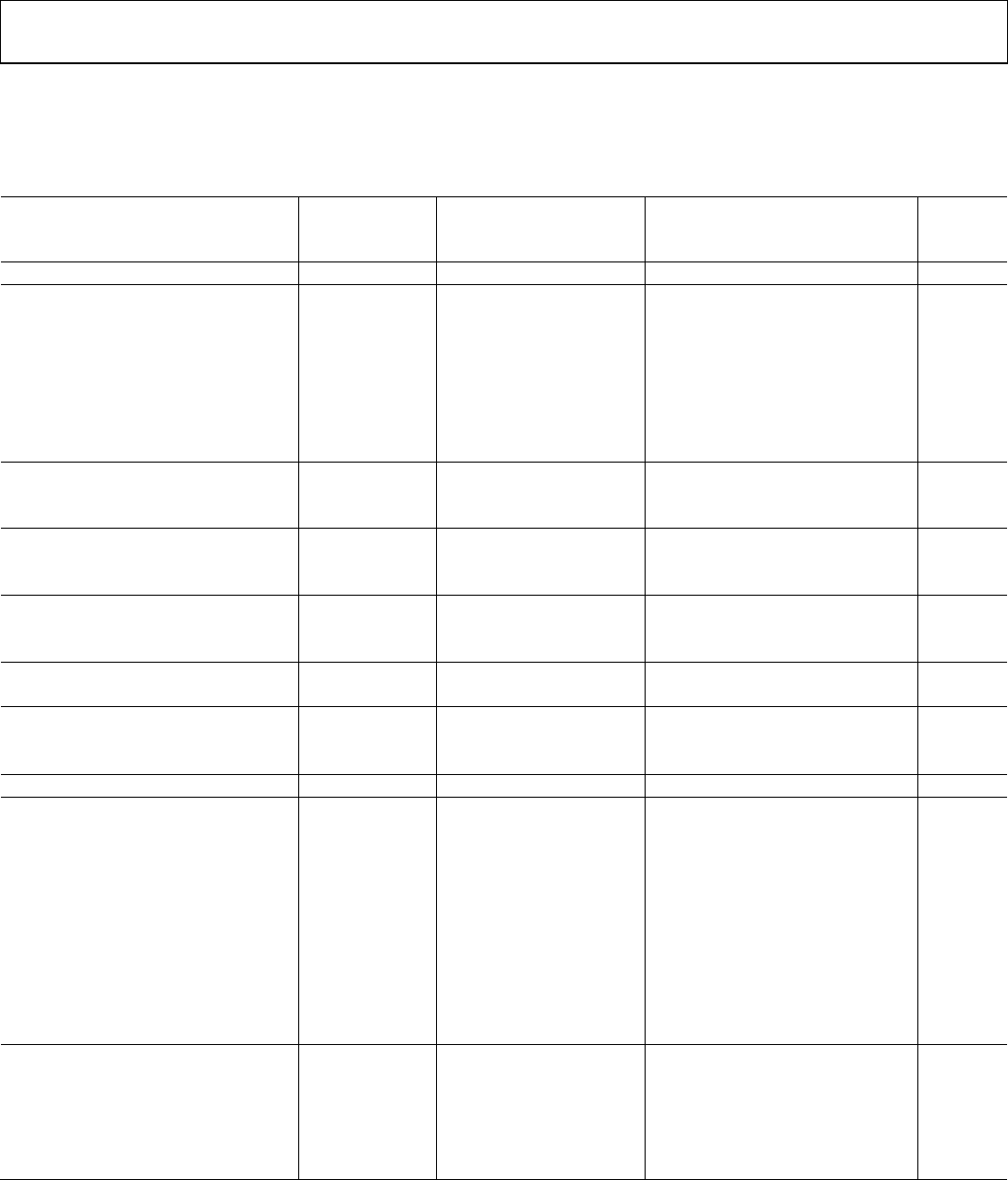

ADC DC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ-125, AD9640ABCPZ-150, AND AD9640BCPZ-150

AVDD = 1.8 V, DVDD = 1.8 V, DRVDD = 3.3 V, maximum sample rate, VIN = −1.0 dBFS differential input, 1.0 V internal reference,

DCS enabled, fast detect outputs disabled, and signal monitor disabled, unless otherwise noted.

Table 2.

Parameter Temperature

AD9640ABCPZ-125/

AD9640BCPZ-125

AD9640ABCPZ-150/

AD9640BCPZ-150

Unit

Min Typ Max Min Typ Max

RESOLUTION Full 14 14 Bits

ACCURACY

No Missing Codes Full Guaranteed Guaranteed

Offset Error Full ±0.3 ±0.6 ±0.3 ±0.6 % FSR

Gain Error Full ±0.2 ±3.0 ±0.2 ±3.0 % FSR

Differential Nonlinearity (DNL)

1

Full ±0.9 −0.95/+1.5 LSB

25°C ±0.4 −0.4/+0.6 LSB

Integral Nonlinearity (INL)

1

Full ±5.0 ±5.0 LSB

25°C ±2 ±2 LSB

MATCHING CHARACTERISTIC

Offset Error 25°C ±0.4 ±0.7 ±0.4 ±0.7 % FSR

Gain Error 25°C ±0.1 ±0.6 ±0.2 ±0.6 % FSR

TEMPERATURE DRIFT

Offset Error Full ±15 ±15 ppm/°C

Gain Error Full ±95 ±95 ppm/°C

INTERNAL VOLTAGE REFERENCE

Output Voltage Error (1 V Mode) Full ±2 ±15 ±3 ±15 mV

Load Regulation @ 1.0 mA Full 7 7 mV

INPUT REFERRED NOISE

VREF = 1.0 V 25°C 1.3 1.3 LSB rms

ANALOG INPUT

Input Span, VREF = 1.0 V Full 2 2 V p-p

Input Capacitance

2

Full 8 8 pF

VREF INPUT RESISTANCE Full 6 6 kΩ

POWER SUPPLIES

Supply Voltage

AVDD, DVDD Full 1.7 1.8 1.9 1.7 1.8 1.9 V

DRVDD (CMOS Mode) Full 1.7 3.3 3.6 1.7 3.3 3.6 V

DRVDD (LVDS Mode) Full 1.7 1.8 1.9 1.7 1.8 1.9 V

Supply Current

I

AVDD

1, 3

Full 385

470

419

517

mA

I

DVDD

1, 3

Full 42 50 mA

I

DRVDD

1

(3.3 V CMOS)

Full 44 53 mA

I

DRVDD

1

(1.8 V CMOS)

Full 22 27 mA

I

DRVDD

1

(1.8 V LVDS)

56 57

POWER CONSUMPTION

DC Input Full 750 846 820 938 mW

Sine Wave Input

1

(DRVDD = 1.8 V)

Full 810 895 mW

Sine Wave Input

1

(DRVDD = 3.3 V)

Full 910 1000 mW

Standby Power

4

Full 77 77 mW

Power-Down Power Full 2.5 6 2.5 6 mW

1

Measured with a low input frequency, full-scale sine wave, with approximately 5 pF loading on each output bit.

2

Input capacitance refers to the effective capacitance between one differential input pin and AGND. See Figure 8 for the equivalent analog input structure.

3

The maximum limit applies to the combination of I

AVDD

and

IDVDD

currents.

4

Standby power is measured with a dc input and with the CLK pins (CLK+, CLK−) inactive (set to AVDD or AGND).