Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- FUNCTIONAL BLOCK DIAGRAM

- PRODUCT HIGHLIGHTS

- TABLE OF CONTENTS

- REVISION HISTORY

- GENERAL DESCRIPTION

- SPECIFICATIONS

- ADC DC SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ80, AD9640ABCPZ-105, AND AD9640BCPZ-105

- ADC DC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ125, AD9640ABCPZ-150, AND AD9640BCPZ150

- ADC AC SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ80, AD9640ABCPZ-105, AND AD9640BCPZ-105

- ADC AC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ125, AD9640ABCPZ-150, AND AD9640BCPZ 150

- DIGITAL SPECIFICATIONS

- SWITCHING SPECIFICATIONS—AD9640ABCPZ-80, AD9640BCPZ-80, AD9640ABCPZ-105, AND AD9640BCPZ105

- SWITCHING SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ-125, AD9640ABCPZ-150, AND AD9640BCPZ150

- TIMING SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

- EQUIVALENT CIRCUITS

- TYPICAL PERFORMANCE CHARACTERISTICS

- THEORY OF OPERATION

- ADC OVERRANGE AND GAIN CONTROL

- SIGNAL MONITOR

- BUILT-IN SELF-TEST (BIST) AND OUTPUT TEST

- CHANNEL/CHIP SYNCHRONIZATION

- SERIAL PORT INTERFACE (SPI)

- MEMORY MAP

- READING THE MEMORY MAP TABLE

- EXTERNAL MEMORY MAP

- MEMORY MAP REGISTER DESCRIPTION

- Sync Control (Register 0x100)

- Fast Detect Control (Register 0x104)

- Fine Upper Threshold (Register 0x106 and Register 0x107)

- Fine Lower Threshold (Register 0x108 and Register 0x109)

- Signal Monitor DC Correction Control (Register 0x10C)

- Signal Monitor DC Value Channel A (Register 0x10D and Register 0x10E)

- Signal Monitor DC Value Channel B (Register 0x10F and Register 0x110)

- Signal Monitor SPORT Control (Register 0x111)

- Signal Monitor Control (Register 0x112)

- Signal Monitor Period (Register 0x113 to Register 0x115)

- Signal Monitor Result Channel A (Register 0x116 to Register 0x118)

- Signal Monitor Result Channel B (Register 0x119 to Register 0x11B)

- APPLICATIONS INFORMATION

- OUTLINE DIMENSIONS

AD9640

Rev. B | Page 8 of 52

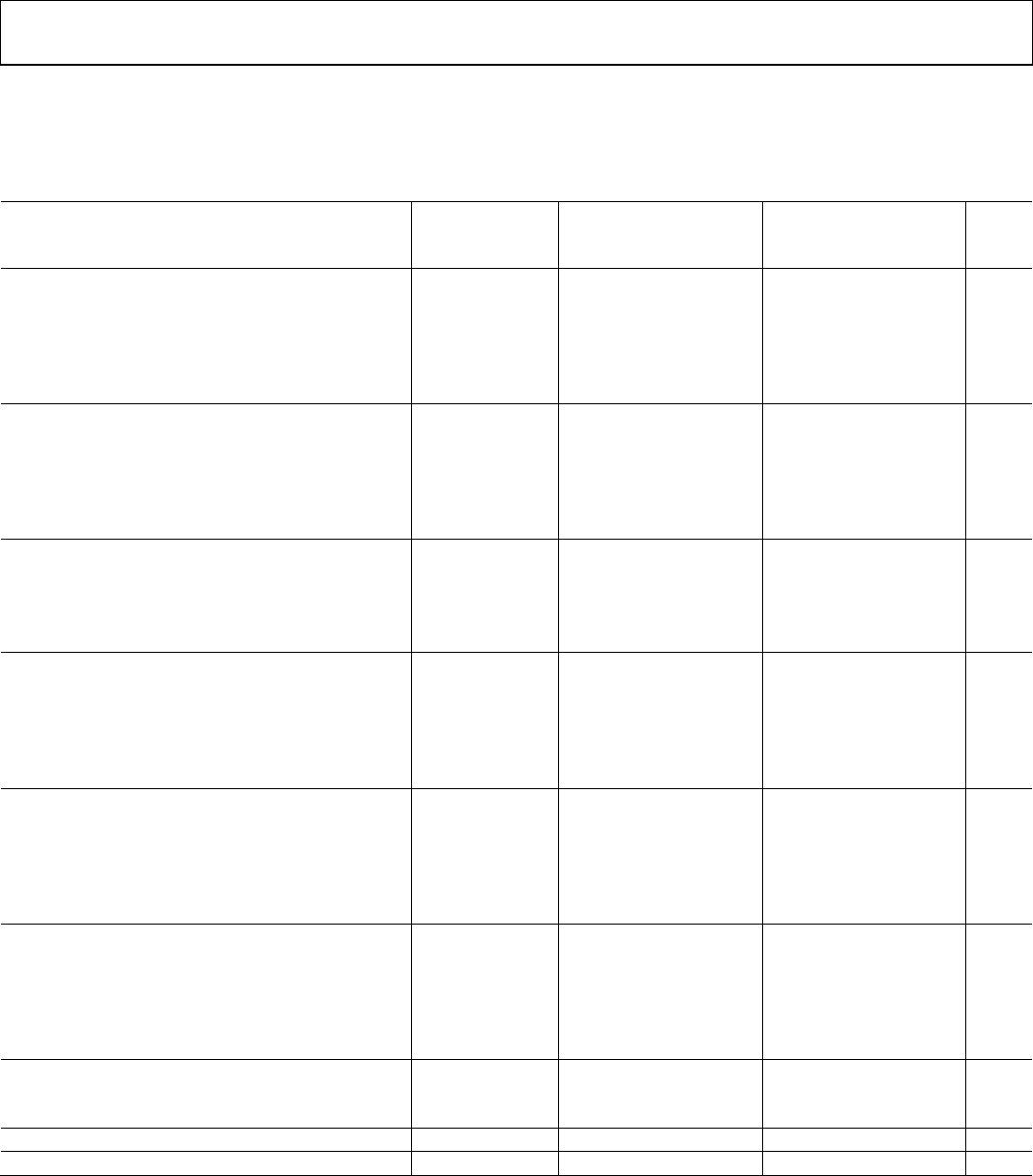

ADC AC SPECIFICATIONS—AD9640ABCPZ-125, AD9640BCPZ-125, AD9640ABCPZ-150, AND AD9640BCPZ 150

AVDD = 1.8 V, DVDD = 1.8 V, DRVDD = 3.3 V, maximum sample rate, VIN = −1.0 dBFS differential input, 1.0 V internal reference,

DCS enabled, fast detect outputs disabled, and signal monitor disabled, unless otherwise noted.

Table 4.

Parameter

1

Temperature

AD9640ABCPZ-125

AD9640BCPZ-125

AD9640ABCPZ-150/

AD9640BCPZ-150

Unit

Min Typ Max Min Typ Max

SIGNAL-TO-NOISE RATIO (SNR)

f

IN

= 2.3 MHz 25°C 72.1 71.9 dB

f

IN

= 70 MHz 25°C 71.8 71.6 dB

Full 70.2 69.5 dB

f

IN

= 140 MHz 25°C 71.4 70.9 dB

f

IN

= 200 MHz 25°C 70.8 70.0 dB

SIGNAL-TO-NOISE AND DISTORTION (SINAD)

f

IN

= 2.3 MHz 25°C 71.8 71.6 dB

f

IN

= 70 MHz 25°C 71.4 71.0 dB

Full 69.5 67.5 dB

f

IN

= 140 MHz 25°C 71.0 70.5 dB

f

IN

= 200 MHz 25°C 70.3 69.9 dB

EFFECTIVE NUMBER OF BITS (ENOB)

f

IN

= 2.3 MHz 25°C 11.8 11.8 Bits

f

IN

= 70 MHz 25°C 11.7 11.8 Bits

f

IN

= 140 MHz 25°C 11.7 11.6 Bits

f

IN

= 200 MHz 25°C 11.6 11.5 Bits

WORST SECOND OR THIRD HARMONIC

f

IN

= 2.3 MHz 25°C −86.5 −86.5 dBc

f

IN

= 70 MHz 25°C −85 −84 dBc

Full −74 −73 dBc

f

IN

= 140 MHz 25°C −84 −83.5 dBc

f

IN

= 200 MHz 25°C −83 −77 dBc

SPURIOUS-FREE DYNAMIC RANGE (SFDR)

f

IN

= 2.3 MHz 25°C 86.5 86.5 dBc

f

IN

= 70 MHz 25°C 85 84 dBc

Full 74 73 dBc

f

IN

= 140 MHz 25°C 84 83.5 dBc

f

IN

= 200 MHz 25°C 83 77 dBc

WORST OTHER HARMONIC OR SPUR

f

IN

= 2.3 MHz 25°C −92 −92 dBc

f

IN

= 70 MHz 25°C −89 −90 dBc

Full −80 −80 dBc

f

IN

= 140 MHz 25°C −89 −90 dBc

f

IN

= 200 MHz 25°C −89 −90 dBc

TWO TONE SFDR

f

IN

= 29.1 MHz, 32.1 MHz (−7 dBFS) 25°C 85 85 dBc

f

IN

= 169.1 MHz, 172.1 MHz (−7 dBFS) 25°C 82 82 dBc

CROSSTALK

2

Full −95 −95 dB

ANALOG INPUT BANDWIDTH 25°C 650 650 MHz

1

See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions.

2

Crosstalk is measured at 100 MHz with −1 dBFS on one channel and no input on the alternate channel.