Datasheet

Table Of Contents

- Description

- Features

- Device Structure

- USE RESTRICTION NOTICE

- 1. Block Diagram and Pin Configuration

- 2. Pixel Signal Output Specifications

- 3. Control Registers

- 3-1 2-wire Serial Communication Operation Specifications

- 3-2 2-wire Serial Communication Register Map (Configuration register, Parameter limit register)

- 3-3 Parameter Limit Registers – [0x1000-0x1FFF] (Read Only and Static)

- 3-4 Manufacturer Specific Registers – [0x3000-0x5FFF ]

- 3-5 Frame Bank A and Bank B specific output samples

- 4. Output Data Format

- 6. On Chip Image Processing

- 7. NVM Memory Map

- 8. How to operate IMX219PQH5-C

- 9. Other Functions

- 10. Electrical Characteristics

- 11. Spectral Sensitivity Characteristic

- 12. Image Sensor Characteristics

- 13. Measurement Method for Image Sensor Characteristics

- 14. Spot Pixel Specification

- 15. Notice on White Pixels Specifications

- 16. Chief Ray Angle Characteristics

- 17. Connection Example

- 18. Notes On Handling

IMX219PQH5-C

33

Index

Byte

Register Name

RW

Comment

Re-Time

Default

(HEX)

Embd

DL

0x028B

[7:0]

COARSE_INTEG_TIME_SHO

RT_B [7:0]

F4

0x028C

[7:0]

CSI_DATA_FORMAT_B [15:8]

RW

CSI-2 data format

frame bank

0A

0x028D

[7:0]

CSI_DATA_FORMAT_B [7:0]

0A

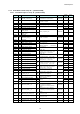

3-2-5 Set-up Registers – [0x0300-0x0627]

3-2-5-1 Clock Set-up Registers – [0x0300-0x0313]

Index

Byte

Register Name

RW

Comment

Re-Time

Default

(HEX)

Embd

DL

0x0300

RW

0x0301

[4:0]

VTPXCK_DIV

RW

vt_pix_clk_div

Video Timing Pixel Clock Divider Value

05

0x0302

RW

0x0303

[1:0]

VTSYCK_DIV

RW

vt_sys_clk_div

Video Timing System Clock Divider Value

1

0x0304

[7:0]

PREPLLCK_VT_DIV

RW

pre_pll_clk_vt_div

Pre PLL clock Video Timing System Divider

Value

values:

Integer-N mode :

prepllck_vt_div = 1, 2, 3

For example

1: EXCK_FREQ 6 MHz to 12 MHz

2: EXCK_FREQ 12 MHz to 24 MHz

3: EXCK_FREQ 24 MHz to 27 MHz

V-sync

2

0x0305

[7:0]

PREPLLCK_OP_DIV

RW

pre_pll_clk_op_div

Pre PLL clock Output System Divider Value

values:

Integer-N mode :

prepllck_vt_div = 1, 2, 3

For example

1: EXCK_FREQ 6 MHz to 12 MHz

2: EXCK_FREQ 12 MHz to 24 MHz

3: EXCK_FREQ 24 MHz to 27 MHz

V-sync

2

0x0306

[2:0]

PLL_VT_MPY[10:8]

RW

pll_vt_multiplier

PLL Video Timing System multiplier Value

V-sync

0

0x0307

[7:0]

PLL_VT_MPY[7:0]

75

0x0308

0x0309

[4:0]

OPPXCK_DIV

RW

op_pix_clk_div

Output Pixel Clock Divider Value

0A

0x030A

RW

0x030B

[1:0]

OPSYCK_DIV

RW

op_sys_clk_div

Output System Clock Divider Value

1

0x030C

[2:0]

PLL_OP_MPY[10:8]

RW

pll_op_multiplier

PLL Output System multiplier Value

V-sync

0

0x030D

[7:0]

PLL_OP_MPY[7:0]

75