Specifications

.

OG_STD-302N-R_v15e Circuit Design, Inc.

11

OPERATION GUIDE

How to calculate the setting values for the PLL register

The PLL IC manual shows that the PLL frequency setting value is obtained with the following equation.

f

vco

= [(M x N)+A] x f

osc

/ R -- Equation 1

f

vco

: Output frequency of external VCO

M: Preset divide ratio of the prescaler (64 or 128)

N: Preset divide ratio of binary 11-bit programmable counter (3 to 2,047)

A: Preset divide ratio of binary 7-bit swallow counter (0 ≤ A ≤ 127 A<N))

f

osc

: Output frequency of the reference frequency oscillator

R: Preset divide ratio of binary 14-bit programmable reference counter (3 to 16,383)

With STD-302N-R, there is an offset frequency (f

offset

) 21.7 MHz for the transmission RF channel frequency f

ch

.

Therefore the expected value of the frequency generated at VCO (f

expect

) is as below.

f

vco

= f

expect

= f

ch

– f

offset ----

Equation 2

The PLL internal circuit compares the phase to the oscillation frequency f

vco.

This phase comparison

frequency (f

comp

) must be decided. f

comp

is made by dividing the frequency input to the PLL from the reference

frequency oscillator by reference counter R. STD-302N-R uses 21.25 MHz for the reference clock f

osc.

f

comp

is

one of 6.25 kHz, 12.5 kHz or 25 kHz.

The above equation 1 results in the following with n = M x N + A, where “n” is the number for division.

f

vco

=n*f

comp

---- Equation 3 n = f

vco

/f

comp

---- Equation 4 note: f

comp

= f

osc

/R

Also, this PLL IC operates with the following R, N, A and M relational expressions.

R=f

osc

/f

comp

---- Equation 5 N = INT (n / M) ---- Equation 6 A = n - (M x N) ---- Equation 7

INT: integer portion of a division.

As an example, the setting value of RF channel frequency f

ch

869.725 MHz can be calculated as below.

The constant values depend on the electronic circuits of STD-302N-R.

Conditions: Channel center frequency: f

ch

= 869.725 MHz

Constant: Offset frequency: f

offset

=21.7 MHz

Constant: Reference frequency: f

osc

=21.25 MHz

Set 25 kHz for Phase comparison frequency and 64 for Prescaler value M

The frequency of VCO will be

f

vco

= f

expect

= f

ch

- f

offset

= 869.725 –21.7 = 848.025MHz

Dividing value “n” is derived from Equation 4

n = f

vco

/ f

comp

= 848.025MHz/25kHz = 33921

Value “R” of the reference counter is derived from Equation 5.

R = f

osc

/f

comp

= 21.25MHz/25kHz = 850

Value “N” of the programmable counter is derived from Equation 6.

N = INT (n/M) = INT(33921/64) = 530

Value “A“ of the swallow counter is derived from Equation 7.

A = n – (M x N) = 33921 – 64 x 530 = 1

The frequency of STD-302N-R is locked at a center frequency f

ch

by inputting the PLL setting values N, A and

R obtained with the above equations as serial data. The above calculations are the same for the other

frequencies.

Excel sheets that contain automatic calculations for the above equations can be found on our web site

(www.cdt21.com/).

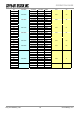

The result of the calculations is arranged as a table in the CPU ROM. The table is read by the channel

change routine each time the channel is changed, and the data is sent to the PLL.