Instruction Manual

76 DS882F1

CS42L73

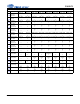

5. REGISTER QUICK REFERENCE

(Default values are shown below the bit names)

I²C Address: 1001010[R/W]—10010100 = 0x94(Write); 10010101 = 0x95(Read)

Adr.

Function

76543210

00h

Fast Mode

Enable.

FM_EN7 FM_EN6 FM_EN5 FM_EN4 FM_EN3 FM_EN2 FM_EN1 FM_EN0

p81

00000000

01h

Device ID A and

B (Read Only).

DEVIDA3 DEVIDA2 DEVIDA1 DEVIDA0 DEVIDB3 DEVIDB2 DEVIDB1 DEVIDB0

p81

01000010

02h

Device ID C and

D

(Read Only).

DEVIDC3 DEVIDC2 DEVIDC1 DEVIDC0 DEVIDD3 DEVIDD2 DEVIDD1 DEVIDD0

p81

10100111

03h

Device ID E

(Read Only)

.

DEVIDE3 DEVIDE2 DEVIDE1 DEVIDE0 Reserved Reserved Reserved Reserved

p81

00110000

04h

Reserved.

Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved

-

0000xxxx

05h

Rev ID (Read

Only)

.

AREVID3 AREVID2 AREVID1 AREVID0 MTLREVID3 MTLREVID2 MTLREVID1 MTLREVID0

p81

xxxxxxxx

06h

Power Ctl 1.

PDN_ADCB PDN_DMICB PDN_ADCA PDN_DMICA Reserved Reserved DISCHG_FILT PDN

p82

11110001

07h

Power Ctl 2.

PDN_MIC2_

BIAS

PDN_MIC1_

BIAS

Reserved PDN_VSP PDN_

ASPSDOUT

PDN_

ASPSDIN

PDN_

XSPSDOUT

PDN_

XSPSDIN

p83

11011111

08h

Power Ctl 3,

Thermal Over-

load Threshold.

THMOVLD_

THLD1

THMOVLD_

THLD0

PDN_THMS PDN_SPKLO PDN_EAR PDN_SPK PDN_LO PDN_HP

p84

00111111

09h

Charge Pump

Freq. and Class

H Control.

CHGFREQ3 CHGFREQ2 CHGFREQ1 CHGFREQ0 Reserved ADPTPWR2 ADPTPWR1 ADPTPWR0

p85

01010000

0Ah

Output Load,

Mic Bias, and

MIC2 Short

Detect Config.

Reserved VP_MIN SPK_LITE_

LOAD

MIC_BIAS_

CTRL

SDET_AMUTE Reserved Reserved Reserved

p86

01010011

0Bh

Digital Mic and

Master Clock

Control.

DMIC_SCLK_

DIV

Reserved Reserved MCLKSEL MCLKDIV2 MCLKDIV1 MCLKDIV0 MCLKDIS

p87

00000000

0Ch

XSP Control.

3ST_XSP XSPDIF X_PCM_

MODE1

X_PCM_

MODE0

X_PCM_BIT_

ORDER

Reserved X_SCK=MCK1 X_SCK=MCK0

p88

00000000

0Dh

XSP Master

Mode Clocking

Control.

X_M/S

Reserved X_MMCC5 X_MMCC4 X_MMCC3 X_MMCC2 X_MMCC1 X_MMCC0

p89

00010101

0Eh

ASP Control.

3ST_ASP Reserved ASPFS3 ASPFS2 ASPFS1 ASPFS0 A_SCK=MCK1 A_SCK=MCK0

p89

00000000

0Fh

ASP Master

Mode Clocking

Control.

A_M/S

Reserved A_MMCC5 A_MMCC4 A_MMCC3 A_MMCC2 A_MMCC1 A_MMCC0

p90

00010101

10h

VSP Control.

3ST_VSP VSPDIF V_PCM_

MODE1

V_PCM_

MODE0

V_PCM_BIT_

ORDER

V_SDIN_LOC V_SCK=MCK1 V_SCK=MCK0

p91

00000000

11h

VSP Master

Mode Clocking

Control.

V_M/S

Reserved V_MMCC5 V_MMCC4 V_MMCC3 V_MMCC2 V_MMCC1 V_MMCC0

p92

00010101

12h

VSP and XSP

Sample Rate.

VSPFS3 VSPFS2 VSPFS1 VSPFS0 XSPFS3 XSPFS2 XSPFS1 XSPFS0

p93

00000000

13h

Misc. Input and

Output Path

Control.

D_SWAP_

MONO_CTL1

D_SWAP_

MONO_CTL0

IPB=A PGAB=A PGASFT ANLGZC DIGSFT ANLGOSFT

p94

00000110

14h

ADC/IP Control.

PGABMUX BOOSTB INV_ADCB IPBMUTE PGAAMUX BOOSTA INV_ADCA IPAMUTE

p97

00000000