User's Manual

Table Of Contents

- 1.1 Overview

- 1.2 General Parameters

- 1.3 Electrical and Thermal Characteristics

- 1.4 Pinout Diagram

- 1.5 Pinout Listing

- 1.6 Package Description

- 1.7 System Design Information

- 1.8 Ordering Information

- A.1 Package Environmental, Operation, Shipment, A....

- A.2 Card Assembly Recommendations

6 603 Hardware Specifications, REV 2

Preliminary—Subject to Change without Notice

1.3.2 AC Electrical Characteristics

This section provides the clock and AC electrical characteristics for the 603.

1.3.2.1 Clock AC Specifications

Table 5 provides the clock AC timing specifications as defined in Figure 1. These specifications are for 25,

33.33, 40, 50, and 66.67 MHz bus clock (SYSCLK) frequencies.

Nap Mode

1

1:1 Typical

160 mW

2:1 Typical

140 160 mW

Sleep Mode

1

1:1 Typical

125 mW

2:1 Typical

110 130 mW

Sleep Mode—PLL Disabled

1

1:1 Typical

70 mW

2:1 Typical

30 40 mW

Sleep Mode—PLL and SYSCLK Disabled

1

1:1 Typical

2.0 mW

2:1 Typical

2.0 2.0 mW

Note

: 1. The values provided for this mode do not include pad driver power (OVDD) or analog supply power

(AVDD). Worst-case AVDD = 15 mW.

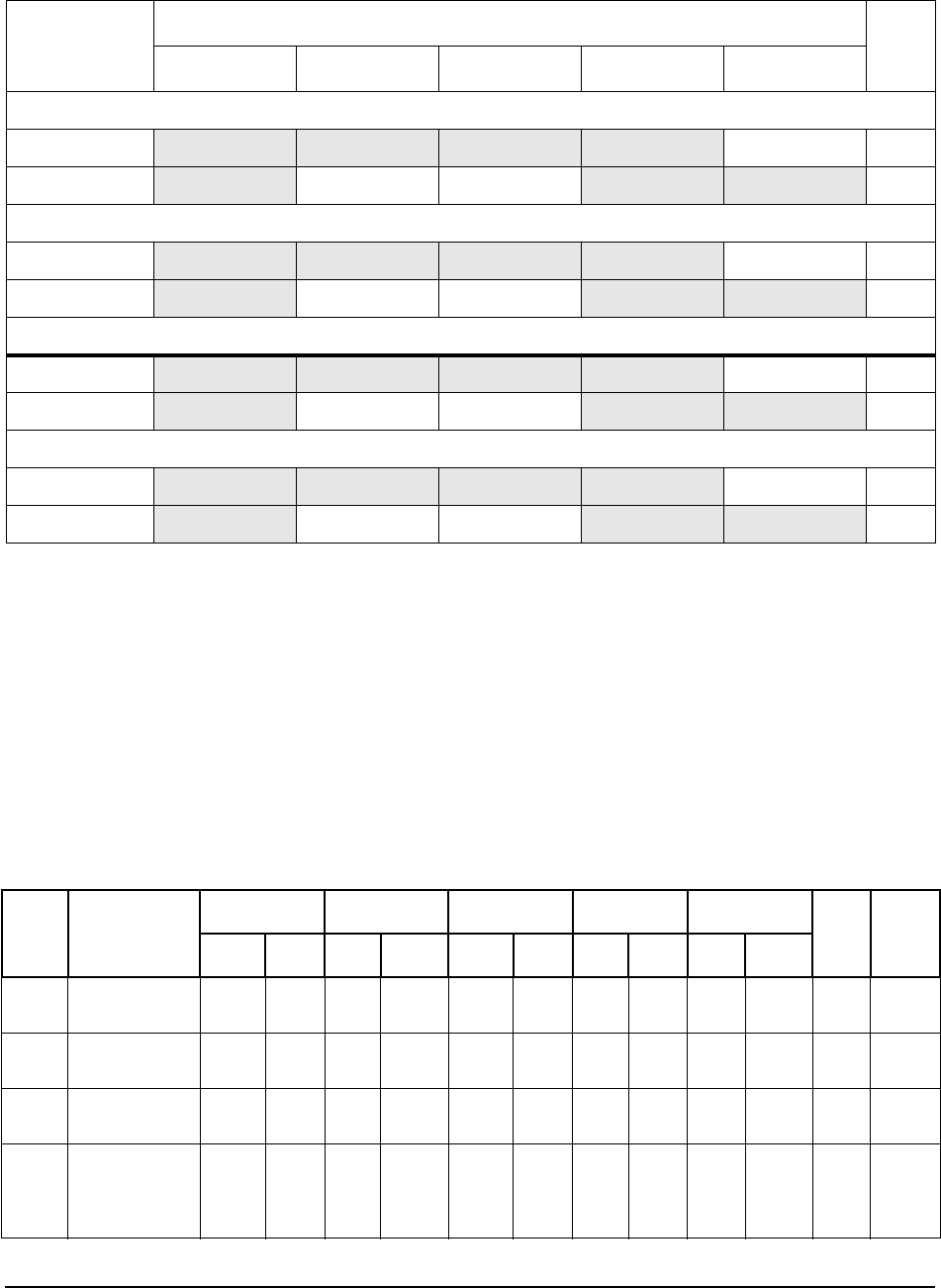

Table 5. Clock AC Timing Specifications

Vdd = 3.3

±

5% V dc, GND = 0 V dc

,

0

≤

T

J

≤

105

°

C

Num Characteristic

25 MHz 33.33 MHz 40 MHz 50 MHz 66.67

Unit Notes

Min Max Min Max Min Max Min Max Min Max

Frequency of

operation

16.67 25.0 25.0 33.33 33.33 40.0 40.0 50.0 50.0 66.67 MHz

1 SYSCLK cycle

time

40.0 60.0 30.0 40.0 25.0 30.0 20.0 25.0 15.0 20.0 ns

2,3 SYSCLK rise

and fall time

— 2.0 — 2.0 — 2.0 — 2.0 — 2.0 ns 1

4 SYSCLK duty

cycle

measured at

1.4 V

40.0 60.0 40.0 60.0 40.0 60.0 40.0 60.0 40.0 60.0 % 3

Table 4. Power Dissipation (Continued)

Vdd = 3.3

±

5% V dc, GND = 0 V dc, 0

≤

T

j

≤

105

°

C

CPU Clock:

SYSCLK

Bus Frequency (SYSCLK)

Unit

25 MHz 33 MHz 40 MHz 50 MHz 66 MHz