Programmable Skew Clock Buffer Specification Sheet

Table Of Contents

- Features

- Functional Description

- Logic Block Diagram

- Pin Configuration

- Pin Definitions

- Block Diagram Description

- Test Mode

- Maximum Ratings

- Operating Range

- Electrical Characteristics

- Capacitance

- AC Test Loads and Waveforms

- Switching Characteristics

- AC Timing Diagrams

- Operational Mode Descriptions

- Ordering Information

- Military Specifications

- DC Characteristics

- Package Diagrams

- Document History

CY7B991

CY7B992

Document Number: 38-07138 Rev. *B Page 2 of 19

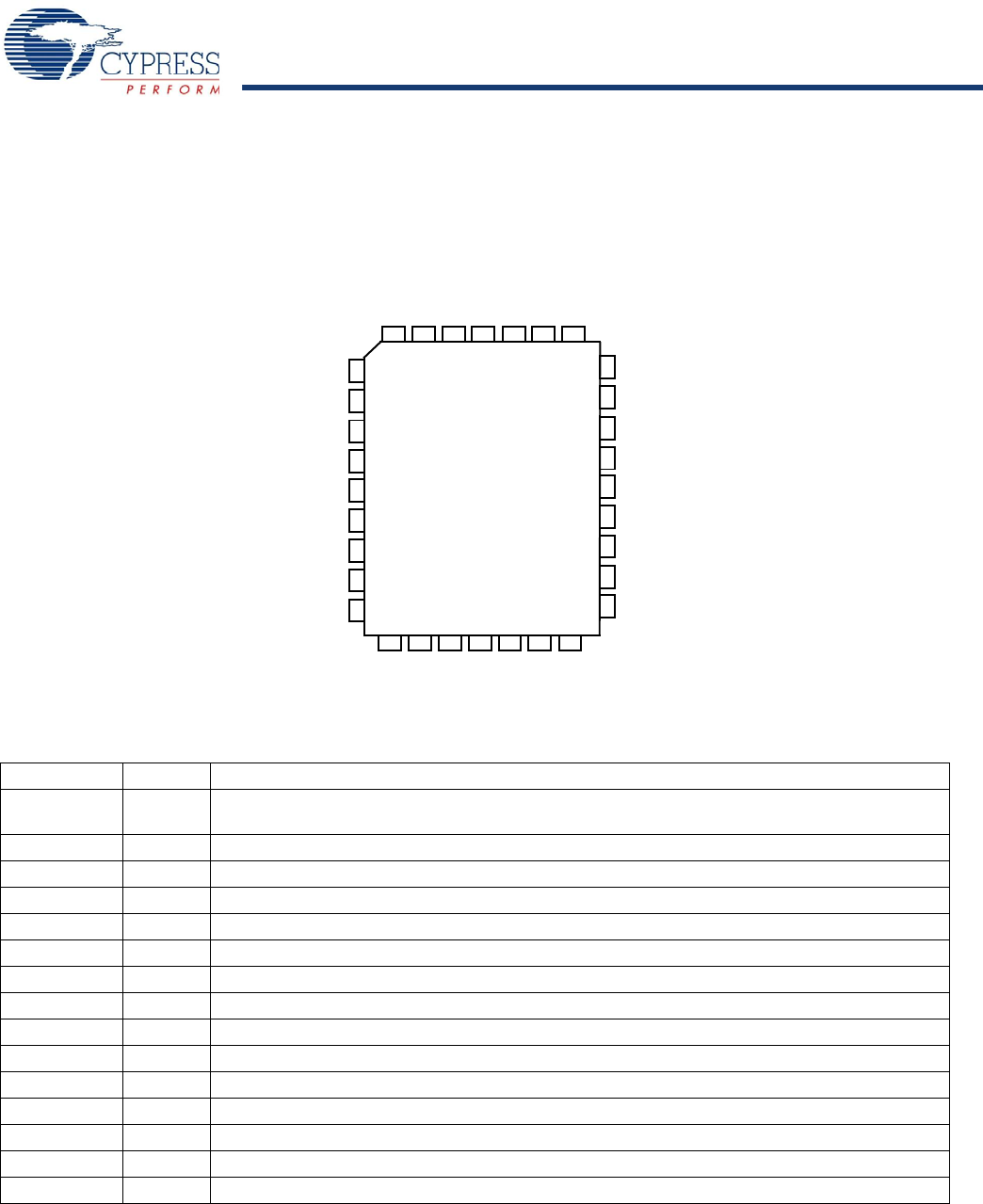

Pin Configuration

Pin Definitions

Signal Name IO Description

REF I Reference frequency input. This input supplies the frequency and timing against which all functional

variations are measured.

FB I PLL feedback input (typically connected to one of the eight outputs).

FS I Three level frequency range select. See Table 1.

1F0, 1F1 I Three level function select inputs for output pair 1 (1Q0, 1Q1). See Table 2.

2F0, 2F1 I Three level function select inputs for output pair 2 (2Q0, 2Q1). See Table 2.

3F0, 3F1 I Three level function select inputs for output pair 3 (3Q0, 3Q1). See Table 2.

4F0, 4F1 I Three level function select inputs for output pair 4 (4Q0, 4Q1). See Table 2.

TEST I Three level select. See “Test Mode” on page 4 under the “Block Diagram Description” on page 3.

1Q0, 1Q1 O Output pair 1. See Table 2.

2Q0, 2Q1 O Output pair 2. See Table 2.

3Q0, 3Q1 O Output pair 3. See Table 2.

4Q0, 4Q1 O Output pair 4. See Table 2.

V

CCN

PWR Power supply for output drivers.

V

CCQ

PWR Power supply for internal circuitry.

GND PWR Ground.

1234323130

17161514 18 19 20

5

6

7

8

9

10

11

12

13

29

28

27

26

25

24

23

22

21

3F0

FS

V

REF

GND

TEST

2F1

FB

2Q1

2Q0

CCQ

2F0

GND

1F1

1F0

V

CCN

1Q0

1Q1

GND

GND

3Q1

3Q0

CCN

V

CCN

V

3F1

4F0

4F1

V

CCQ

V

CCN

4Q1

4Q0

GND

GND

PLCC/LCC

CY7B991

CY7B992

[+] Feedback