Programmable Skew Clock Buffer Specification Sheet

Table Of Contents

- Features

- Functional Description

- Logic Block Diagram

- Pin Configuration

- Pin Definitions

- Block Diagram Description

- Test Mode

- Maximum Ratings

- Operating Range

- Electrical Characteristics

- Capacitance

- AC Test Loads and Waveforms

- Switching Characteristics

- AC Timing Diagrams

- Operational Mode Descriptions

- Ordering Information

- Military Specifications

- DC Characteristics

- Package Diagrams

- Document History

CY7B991

CY7B992

Document Number: 38-07138 Rev. *B Page 9 of 19

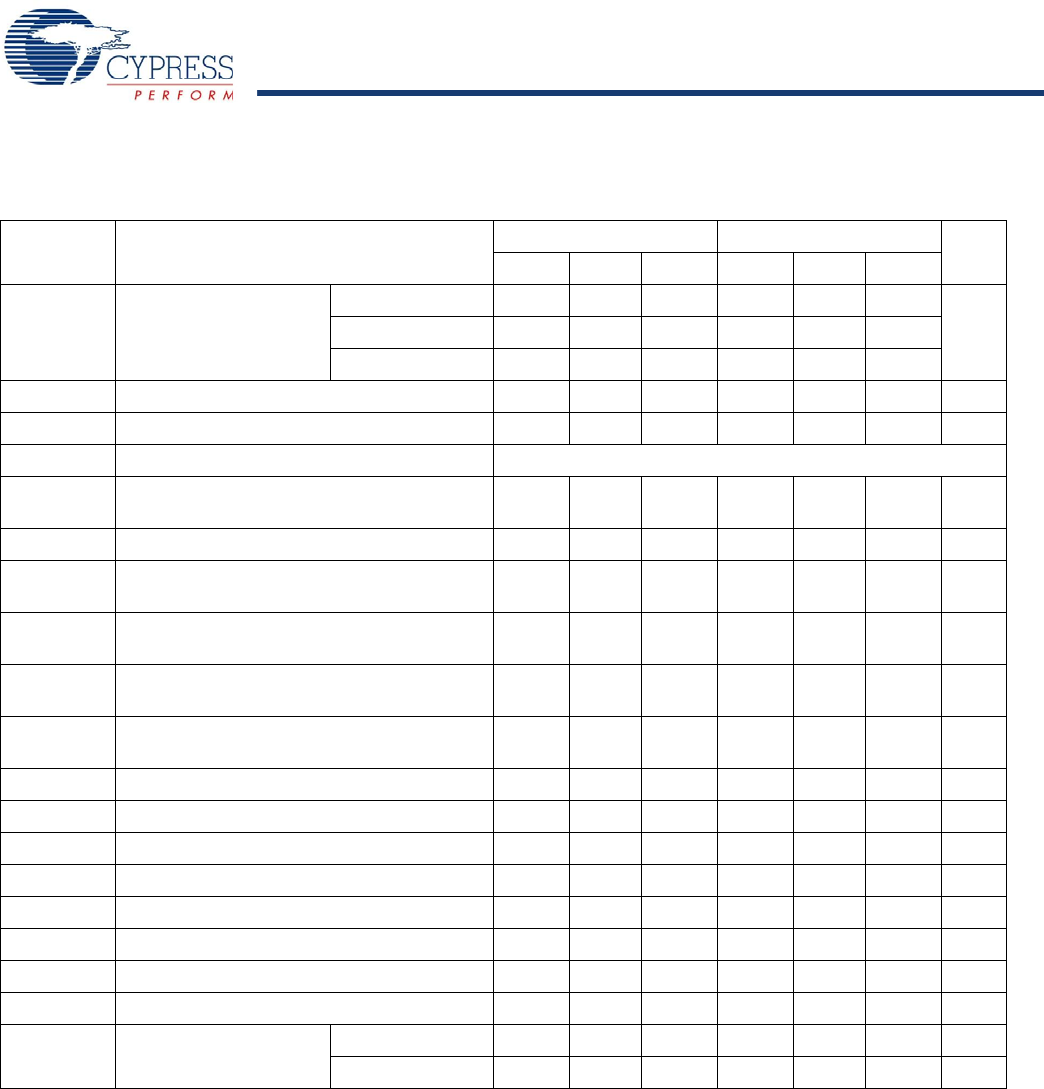

Switching Characteristics

Over the Operating Range

[2, 13]

(continued)

CY7B991–5 CY7B992–5

Parameter Description Min Typ Max Min Typ Max Unit

f

NOM

Operating Clock

Frequency in MHz

FS = LOW

[1, 2]

15 30 15 30 MHz

FS = MID

[1, 2]

25 50 25 50

FS = HIGH

[1, 2 , 3]

40 80 40 80

[15]

t

RPWH

REF Pulse Width HIGH 5.0 5.0 ns

t

RPWL

REF Pulse Width LOW 5.0 5.0 ns

t

U

Programmable Skew Unit See Table 1

t

SKEWPR

Zero Output Matched-Pair Skew

(XQ0, XQ1)

[16, 17]

0.1 0.25 0.1 0.25 ns

t

SKEW0

Zero Output Skew (All Outputs)

[16, 18]

0.25 0.5 0.25 0.5 ns

t

SKEW1

Output Skew (Rise-Rise, Fall-Fall, Same

Class Outputs)

[16, 19]

0.6 0.7 0.6 0.7 ns

t

SKEW2

Output Skew (Rise-Fall, Nominal-Inverted,

Divided-Divided)

[16, 19]

0.5 1.0 0.6 1.5 ns

t

SKEW3

Output Skew (Rise-Rise, Fall-Fall, Different

Class Outputs)

[16, 19]

0.5 0.7 0.5 0.7 ns

t

SKEW4

Output Skew (Rise-Fall, Nominal-Divided,

Divided-Inverted)

[16, 19]

0.5 1.0 0.6 1.7 ns

t

DEV

Device-to-Device Skew

[14, 21]

1.25 1.25 ns

t

PD

Propagation Delay, REF Rise to FB Rise –0.5 0.0 +0.5 –0.5 0.0 +0.5 ns

t

ODCV

Output Duty Cycle Variation

[22]

–1.0 0.0 +1.0 –1.2 0.0 +1.2 ns

t

PWH

Output HIGH Time Deviation from 50%

[23, 24]

2.5 4.0 ns

t

PWL

Output LOW Time Deviation from 50%

[23, 24]

3 4.0 ns

t

ORISE

Output Rise Time

[23, 25]

0.15 1.0 1.5 0.5 2.0 3.5 ns

t

OFALL

Output Fall Time

[23, 25]

0.15 1.0 1.5 0.5 2.0 3.5 ns

t

LOCK

PLL Lock Time

[26]

0.5 0.5 ms

t

JR

Cycle-to-Cycle Output

Jitter

RMS

[14]

25 25 ps

Peak-to-Peak

[14]

200 200 ps

[+] Feedback