18-Mbit Burst of 2 Pipelined SRAM with QDRTM Architecture Specification Sheet

CY7C1306BV25

CY7C1303BV25

Document #: 38-05627 Rev. *A Page 2 of 19

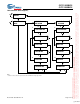

512Kx18

CLK

A

(18:0)

Gen.

K

K

Control

Logic

Address

Register

D

[17:0]

Read Add. Decode

Read Data Reg.

RPS

WPS

Q

[17:0]

Control

Logic

Address

Register

Reg.

Reg.

Reg.

18

19

18

36

Write

18

BWS

0

Vref

Write Add. Decode

Data Reg

Write

Data Reg

Memory

Array

512Kx18

Memory

Array

18

18

A

(18:0)

19

18

C

C

BWS

1

Logic Block Diagram (CY7C1303BV25)

256Kx36

CLK

A

(17:0)

Gen.

K

K

Control

Logic

Address

Register

D

[35:0]

Read Add. Decode

Read Data Reg.

RPS

WPS

Q

[35:0]

Control

Logic

Address

Register

Reg.

Reg.

Reg.

36

18

36

72

Write

36

BWS

0

Vref

Write Add. Decode

Data Reg

Write

Data Reg

Memory

Array

256Kx36

Memory

Array

36

36

A

(17:0)

18

36

C

C

BWS

1

BWS

2

BWS

3

Logic Block Diagram (CY7C1306BV25)

Selection Guide

CY7C1303BV25-167

CY7C1306BV25-167 Unit

Maximum Operating Frequency 167 MHz

Maximum Operating Current 500 mA

[+] Feedback