Transceiver with Reclocker Specification Sheet

CYV15G0404DXB

Document #: 38-02097 Rev. *B Page 3 of 44

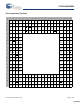

Shifter

TXLBA

TXLBC

Transmit Path Block Diagram

TXRATEA

Input

Register

Phase-Align

Buffer

Encoder

BIST LFSR

SPDSELA

REFCLKA+

REFCLKA–

Transmit PLL

Clock Multiplier

TXCLKA

Bit-Rate Clock

Character-Rate Clock A

OUTA1+

OUTA1–

OUTA2+

OUTA2–

8

TXRATEB

Input

Register

Phase-Align

Buffer

Encoder

BIST LFSR

Shifter

SPDSELB

REFCLKB+

REFCLKB–

Bit-Rate Clock

Character-Rate Clock B

OUTB1+

OUTB1–

OUTB2+

OUTB2–

Input

Register

Phase-Align

Buffer

8B/10B

BIST LFSR

Transmit PLL

Clock Multiplier A

Input

Register

Phase-Align

Buffer

8B/10B

BIST LFSR

Shifter

TXCLKB

TXRATEC

Input

Register

Phase-Align

Buffer

8B/10B

BIST LFSR

SPDSELC

REFCLKC+

REFCLKC–

TXCLKC

Bit-Rate Clock

Character-Rate Clock C

TXRATED

Input

Register

Phase-Align

Buffer

8B/10B

BIST LFSR

Shifter

SPDSELD

REFCLKD+

REFCLKD–

Transmit PLL

Clock Multiplier D

TXCLKD

Bit-Rate Clock

Character-Rate Clock D

OUTD1+

OUTD1–

OUTD2+

OUTD2–

OUTC1+

OUTC1–

OUTC2+

OUTC2–

TXCTA[1:0]

TXDD[7:0]

OEA[2..1]

TXBIST

ENCBYPA

TXCKSELA

= Internal Signal

TXERRA

TXERRB

TXERRD

TXERRC

TXCLKOA

TXCLKOB

TXCLKOC

TXCLKOD

TXDA[7:0]

2

TXDB[7:0]

8

2

TXCTB[1:0]

8

2

TXDC[7:0]

TXCTC[1:0]

8

2

TXCTD[1:0]

10

10

10

10

10 10 10 10

10

10

10 10

10 10

10

10

A

ENCBYPB

ENCBYPC

ENCBYPD

TXBIST

B

TXBIST

C

TXBISTD

OEB[2..1]

OEC[2..1]

OED[2..1]

PABRSTA

PABRSTB

PABRSTC

PABRSTD

OEA[2..1]

OEB[2..1]

OEC[2..1]

OED[2..1]

TXLBD

Shifter

TXLBB

Transmit PLL

Clock Multiplier B

Transmit PLL

Clock Multiplier C

10

TXCKSELB

0

TXCKSELC

10

TXCKSELD

10

RECLCK[A..D] are Internal Reclocker Signals

Encoder

Encoder

Encoder

Encoder

1

RECLCKA

RECLCKB

RECLCKC

RECLCKD

TXLB[A..D] are Internal Serial Loopback Signals

[+] Feedback [+] Feedback