Full Speed USB Controller Specification Sheet

CY7C64215

Document 38-08036 Rev. *C Page 11 of 30

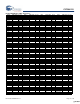

Register Map Bank 0 Table: User Space

Name Addr (0,Hex) Access Name Addr (0,Hex) Access Name Addr (0,Hex) Access Name Addr (0,Hex) Access

PRT0DR

00 RW PMA0_DR 40 RW

ASC10CR0

80

RW

C0

PRT0IE

01 RW PMA1_DR 41 RW

ASC10CR1

81

RW

C1

PRT0GS

02 RW PMA2_DR 42 RW

ASC10CR2

82

RW

C2

PRT0DM2

03 RW PMA3_DR 43 RW

ASC10CR3

83

RW

C3

PRT1DR

04 RW PMA4_DR 44 RW

ASD11CR0

84

RW

C4

PRT1IE

05 RW PMA5_DR 45 RW

ASD11CR1

85

RW

C5

PRT1GS

06 RW PMA6_DR 46 RW

ASD11CR2

86

RW

C6

PRT1DM2

07 RW PMA7_DR 47 RW

ASD11CR3

87

RW

C7

PRT2DR

08 RW USB_SOF0 48 R 88 C8

PRT2IE

09 RW USB_SOF1 49 R 89 C9

PRT2GS

0A RW USB_CR0 4A RW 8A CA

PRT2DM2

0B RW USBIO_CR0 4B # 8B CB

PRT3DR

0C

RW

USBIO_CR1 4C RW 8C CC

PRT3IE

0D

RW

4D 8D CD

PRT3GS

0E

RW

EP1_CNT1 4E # 8E CE

PRT3DM2

0F

RW

EP1_CNT 4F RW 8F CF

PRT4DR

10

RW

EP2_CNT1 50 #

ASD20CR0

90

RW CUR_PP

D0

RW

PRT4IE

11

RW

EP2_CNT 51 RW

ASD20CR1

91

RW STK_PP

D1

RW

PRT4GS

12

RW

EP3_CNT1 52 #

ASD20CR2

92

RW

D2

PRT4DM2

13

RW

EP3_CNT 53 RW

ASD20CR3

93

RW IDX_PP

D3

RW

PRT5DR

14

RW

EP4_CNT1 54 #

ASC21CR0

94

RW MVR_PP

D4

RW

PRT5IE

15

RW

EP4_CNT 55 RW

ASC21CR1

95

RW MVW_PP

D5

RW

PRT5GS

16

RW

EP0_CR 56 #

ASC21CR2

96

RW I2C_CFG

D6

RW

PRT5DM2

17

RW

EP0_CNT 57 #

ASC21CR3

97

RW I2C_SCR

D7

#

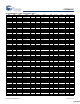

18 EP0_DR0 58 RW 98

I2C_DR

D8

RW

19 EP0_DR1 59 RW 99

I2C_MSCR

D9

#

1A EP0_DR2 5A RW 9A

INT_CLR0

DA

RW

1B EP0_DR3 5B RW 9B

INT_CLR1

DB

RW

PRT7DR

1C

RW

EP0_DR4 5C RW 9C

INT_CLR2

DC

RW

PRT7IE

1D

RW

EP0_DR5 5D RW 9D

INT_CLR3

DD

RW

PRT7GS

1E

RW

EP0_DR6 5E RW 9E

INT_MSK3

DE

RW

PRT7DM2

1F

RW

EP0_DR7 5F RW 9F

INT_MSK2

DF

RW

DBB00DR0

20

# AMX_IN

60

RW

A0

INT_MSK0

E0

RW

DBB00DR1

21

W AMUXCFG

61

RW

A1

INT_MSK1

E1

RW

DBB00DR2

22

RW

62 A2

INT_VC

E2

RC

DBB00CR0

23

# ARF_CR

63

RW

A3

RES_WDT

E3

W

DBB01DR0

24

# CMP_CR0

64

#

A4

DEC_DH

E4

RC

DBB01DR1

25

W ASY_CR

65

#

A5

DEC_DL

E5

RC

DBB01DR2

26

RW CMP_CR1

66

RW

A6

DEC_CR0

E6

RW

DBB01CR0

27

#

67 A7

DEC_CR1

E7

RW

DCB02DR0

28

#

68

MUL1_X

A8

W

MUL0_X

E8

W

DCB02DR1

29

W

69

MUL1_Y

A9

W

MUL0_Y

E9

W

DCB02DR2

2A

RW

6A

MUL1_DH

AA

R

MUL0_DH

EA

R

DCB02CR0

2B

#

6B

MUL1_DL

AB

R

MUL0_DL

EB

R

DCB03DR0

2C

# TMP_DR0

6C

RW

ACC1_DR1

AC

RW

ACC0_DR1

EC

RW

DCB03DR1

2D

W TMP_DR1

6D

RW

ACC1_DR0

AD

RW

ACC0_DR0

ED

RW

DCB03DR2

2E

RW TMP_DR2

6E

RW

ACC1_DR3

AE

RW

ACC0_DR3

EE

RW

DCB03CR0

2F

# TMP_DR3

6F

RW

ACC1_DR2

AF

RW

ACC0_DR2

EF

RW

30

ACB00CR3

70

RW

RDI0RI

B0

RW

F0

31

ACB00CR0

71

RW

RDI0SYN

B1

RW

F1

32

ACB00CR1

72

RW

RDI0IS

B2

RW

F2

33

ACB00CR2

73

RW

RDI0LT0

B3

RW

F3

34

ACB01CR3

74

RW

RDI0LT1

B4

RW

F4

35

ACB01CR0

75

RW

RDI0RO0

B5

RW

F5

36

ACB01CR1

76

RW

RDI0RO1

B6

RW

F6

37

ACB01CR2

77

RW

B7

CPU_F

F7

RL

38

78 B8 F8

39

79 B9 F9

3A

7A BA FA

3B

7B BB FB

3C

7C BC FC

3D

7D BD

DAC_D

FD

RW

3E

7E BE

CPU_SCR1

FE

#

3F

7F BF

CPU_SCR0

FF

#

Blank fields are Reserved and should not be accessed. # Access is bit specific.

[+] Feedback [+] Feedback