Independent Clock Deserializing Reclocker Specification Sheet

CYV15G0404RB

Document #: 38-02102 Rev. *C Page 22 of 27

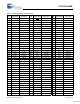

CYV15G0404RB Device RESET Characteristics Over the Operating Range

t

RST

Device RESET Pulse Width 30 ns

CYV15G0404RB Reclocker Serial Output Characteristics Over the Operating Range

Parameter Description Condition Min. Max. Unit

t

B

Bit Time 5128 660 ps

t

RISE

[14]

CML Output Rise Time 20−80% (CML Test Load) SPDSELx = HIGH 50 270 ps

SPDSELx = MID 100 500 ps

SPDSELx =LOW 180 1000 ps

t

FALL

[14]

CML Output Fall Time 80−20% (CML Test Load) SPDSELx = HIGH 50 270 ps

SPDSELx = MID 100 500 ps

SPDSELx =LOW 180 1000 ps

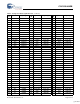

CYV15G0404RB AC Electrical Characteristics (continued)

Parameter Description Min Max Unit

PLL Characteristics

Parameter Description Condition Min Typ Max Unit

CYV15G0404RB Reclocker Output PLL Characteristics

t

JRGENSD

[14, 22]

Reclocker Jitter Generation - SD Data Rate TRGCLKx = 27 MHz 133 ps

t

JRGENHD

[14, 22]

Reclocker Jitter Generation - HD Data Rate TRGCLKx = 148.5 MHz 107 ps

CYV15G0404RB Receive PLL Characteristics Over the Operating Range

t

RXLOCK

Receive PLL Lock to Input Data Stream (cold start) 376k UI

Receive PLL Lock to Input Data Stream 376k UI

t

RXUNLOCK

Receive PLL Unlock Rate 46 UI

Note

22. Receiver input stream is BIST data from the transmit channel. This data is reclocked and output to a wide bandwidth digital sampling oscilloscope. The

measurement was recorded after 10,000 histogram hits, time referenced to REFCLKx± of the transmit channel.

Capacitance

[14]

Parameter Description Test Conditions Max Unit

C

INTTL

TTL Input Capacitance T

A

= 25°C, f

0

= 1 MHz, V

CC

= 3.3V 7 pF

C

INPECL

PECL input Capacitance T

A

= 25°C, f

0

= 1 MHz, V

CC

= 3.3V 4 pF

[+] Feedback