Independent Clock Deserializing Reclocker Specification Sheet

CYV15G0404RB

Document #: 38-02102 Rev. *C Page 24 of 27

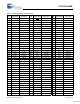

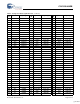

Table 6. Package Coordinate Signal Allocation

Ball

ID

Signal Name Signal Type

Ball

ID

Signal Name Signal Type

Ball

ID

Signal Name Signal Type

A01 INC1– CML IN C07 ULCC

LVTTL IN PU F17 VCC POWER

A02 ROUTC1– CML OUT C08 GND GROUND F18 RXDB[0] LVTTL OUT

A03 INC2– CML IN C09 DATA[7] LVTTL IN PU F19 RECLKOB LVTTL OUT

A04 ROUTC2– CML OUT C10 DATA[5] LVTTL IN PU F20 RXDB[1] LVTTL OUT

A05 VCC POWER C11 DATA[3] LVTTL IN PU G01 GND GROUND

A06 IND1– CML IN C12 DATA[1] LVTTL IN PU G02 WREN

LVTTL IN PU

A07 ROUTD1– CML OUT C13 GND GROUND G03 GND GROUND

A08 GND GROUND C14 VCC POWER G04 GND GROUND

A09 IND2– CML IN C15 SPDSELD 3-LEVEL SEL G17 SPDSELB 3-LEVEL SEL

A10 ROUTD2– CML OUT C16 VCC POWER G18 NC NO CONNECT

A11 INA1– CML IN C17 LDTDEN LVTTL IN PU G19 SPDSELA 3-LEVEL SEL

A12 ROUTA1– CML OUT C18 TRST

LVTTL IN PU G20 RXDB[3] LVTTL OUT

A13 GND GROUND C19 GND GROUND H01 GND GROUND

A14 INA2– CML IN C20 TDO LVTTL 3-S OUT H02 GND GROUND

A15 ROUTA2– CML OUT D01 TCLK LVTTL IN PD H03 GND GROUND

A16 VCC POWER D02 RESET

LVTTL IN PU H04 GND GROUND

A17 INB1– CML IN D03 INSELD LVTTL IN H17 GND GROUND

A18 ROUTB1– CML OUT D04 INSELA LVTTL IN H18 GND GROUND

A19 INB2– CML IN D05 VCC POWER H19 GND GROUND

A20 ROUTB2– CML OUT D06 ULCA

LVTTL IN PU H20 GND GROUND

B01 INC1+ CML IN D07 SPDSELC 3-LEVEL SEL J01 GND GROUND

B02 ROUTC1+ CML OUT D08 GND GROUND J02 GND GROUND

B03 INC2+ CML IN D09 DATA[6] LVTTL IN PU J03 GND GROUND

B04 ROUTC2+ CML OUT D10 DATA[4] LVTTL IN PU J04 GND GROUND

B05 VCC POWER D11 DATA[2] LVTTL IN PU J17 BISTSTB LVTTL OUT

B06 IND1+ CML IN D12 DATA[0] LVTTL IN PU J18 RXDB[2] LVTTL OUT

B07 ROUTD1+ CML OUT D13 GND GROUND J19 RXDB[7] LVTTL OUT

B08 GND GROUND D14 GND GROUND J20 RXDB[4] LVTTL OUT

B09 IND2+ CML IN D15 ULCB

LVTTL IN PU K01 RXDC[4] LVTTL OUT

B10 ROUTD2+ CML OUT D16 VCC POWER K02 TRGCLKC– PECL IN

B11 INA1+ CML IN D17 NC NO CONNECT K03 GND GROUND

B12 ROUTA1+ CML OUT D18 VCC POWER K04 GND GROUND

B13 GND GROUND D19 SCANEN2 LVTTL IN PD K17 RXDB[5] LVTTL OUT

B14 INA2+ CML IN D20 TMEN3 LVTTL IN PD K18 RXDB[6] LVTTL OUT

B15 ROUTA2+ CML OUT E01 VCC POWER K19 RXDB[9] LVTTL OUT

B16 VCC POWER E02 VCC POWER K20 LFIB

LVTTL OUT

B17 INB1+ CML IN E03 VCC POWER L01 RXDC[5] LVTTL OUT

B18 ROUTB1+ CML OUT E04 VCC POWER L02 TRGCLKC+ PECL IN

B19 INB2+ CML IN E17 VCC POWER L03 LFIC

LVTTL OUT

[+] Feedback