Independent Clock Deserializing Reclocker Specification Sheet

CYV15G0404RB

Document #: 38-02102 Rev. *C Page 6 of 27

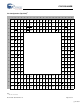

Pin Configuration (Top View)

[1]

Note

1. NC = Do not connect.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

A

IN

C1–

ROUT

C1–

IN

C2–

ROUT

C2–

V

CC

IN

D1–

ROUT

D1–

GND

IN

D2–

ROUT

D2–

IN

A1–

ROUT

A1–

GND

IN

A2–

ROUT

A2–

V

CC

IN

B1–

ROUT

B1–

IN

B2–

ROUT

B2–

B

IN

C1+

ROUT

C1+

IN

C2+

ROUT

C2+

V

CC

IN

D1+

ROUT

D1+

GND

IN

D2+

ROUT

D2+

IN

A1+

ROUT

A1+

GND

IN

A2+

ROUT

A2+

V

CC

IN

B1+

ROUT

B1+

IN

B2+

ROUT

B2+

C

TDI TMS INSELC INSELB

V

CC

ULCD ULCC

GND

DATA

[7]

DATA

[5]

DATA

[3]

DATA

[1]

GND V

CC

SPD

SELD

V

CC

LDTD

EN

TRST

GND

TDO

D

TCLK RESET INSELD INSELA

V

CC

ULCA SPD

SELC

GND

DATA

[6]

DATA

[4]

DATA

[2]

DATA

[0]

GND GND

ULCB

V

CC

NC V

CC

SCAN

EN2

TMEN3

E

V

CC

V

CC

V

CC

V

CC

V

CC

V

CC

V

CC

V

CC

F

RX

DC[8]

RX

DC[9]

V

CC

V

CC

V

CC

RX

DB[0]

RE

CLKOB

RX

DB[1]

G

GND

WREN

GND GND

SPD

SELB

NC

SPD

SELA

RX

DB[3]

H

GND GND GND GND GND GND GND GND

J

GND GND GND GND

BIST

STB

RX

DB[2]

RX

DB[7]

RX

DB[4]

K

RX

DC[4]

TRG

CLKC–

GND GND

RX

DB[5]

RX

DB[6]

RX

DB[9]

LFIB

L

RX

DC[5]

TRG

CLKC+

LFIC

GND

RX

DB[8]

RX

CLKB+

RX

CLKB–

GND

M

RX

DC[6]

RX

DC[7]

V

CC

RE

PDOC

TRG

CLKB+

TRG

CLKB–

RE

PDOB

GND

N

GND GND GND GND GND GND GND GND

P

RX

DC[3]

RX

DC[2]

RX

DC[1]

RX

DC[0]

GND GND GND GND

R

BIST

STC

RE

CLKOC

RX

CLKC+

RX

CLKC–

V

CC

V

CC

V

CC

V

CC

T

V

CC

V

CC

V

CC

V

CC

V

CC

V

CC

V

CC

V

CC

U

V

CC

V

CC

V

CC

V

CC

V

CC

RX

DD[4]

RX

DD[3]

GND GND

ADDR

[0]

TRG

CLKD–

GND GND GND V

CC

V

CC

RX

DA[4]

V

CC

BIST

STA

RX

DA[0]

V

V

CC

V

CC

V

CC

RX

DD[8]

V

CC

RX

DD[5]

RX

DD[1]

GND

BIST

STD

ADDR

[2]

TRG

CLKD+

RE

CLKOA

GND GND V

CC

V

CC

RX

DA[9]

RX

DA[5]

RX

DA[2]

RX

DA[1]

W

V

CC

V

CC

LFID RX

CLKD–

V

CC

RX

DD[6]

RX

DD[0]

GND

ADDR

[3]

ADDR

[1]

RX

CLKA+

RE

PDOA

GND GND V

CC

V

CC

LFIA TRG

CLKA+

RX

DA[6]

RX

DA[3]

Y

V

CC

V

CC

RX

DD[9]

RX

CLKD+

V

CC

RX

DD[7]

RX

DD[2]

GND

RE

CLKOD

NC

GND

RX

CLKA–

GND GND V

CC

V

CC

RE

PDOD

TRG

CLKA–

RX

DA[8]

RX

DA[7]

[+] Feedback