Datasheet

DTM68105B

8GB - 288-Pin 2Rx8 Registered ECC DDR4 DIMM

Document 06394, Revision A, 24-Sep-14, Dataram Corporation © 2014 Page 5

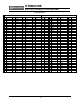

PINDESCRIPTION

Name Function

CB[7:0] Data Check Bits

DQ[63:0] Data Bits

DQS[8:0]_t, DQS[8:0]_c Differential Data Strobes

DM[8:0]_n Data Masks

CK_t[1:0], CK_c[1:0] Differential Clock Inputs

CKE[1:0] Clock Enables

CAS_n / A15 Multiplexed: Column Address Strobe or Address 15

RAS_n / A16 Multiplexed: Row Address Strobe or Address 16

CS[1:0]_n, CS[3:2]* Chip Selects

ACT_n Activate Command Input

WE_n / A14 Multiplexed: Write Enable or Address 14

C[2:0] Chip ID Inputs

A[17:0] Address Inputs

BA[1:0] Bank Address select Inputs

BG[1:0] Bank Group select Inputs

ODT[1:0] On Die Termination Inputs

SA[2:0] SPD Address

SCL SPD Clock Input

SDA SPD Data Input/Output

EVENT_n Temperature Sensing

RESET_n Reset for register and DRAMs

PARITY Parity bit input for Addr/Ctrl

ALERT_n CRC Error Flag or CMD/Addr Parity Flag Output

A12 / BC_n Combination Input: Address12/Burst Chop

A10 / AP Combination Input: Addr10/Auto-precharge

12V* Optional Power Supply*

V

PP

Charge Pump Power

V

SS

Ground

V

DD

Power

V

DDSPD

SPD EEPROM Power

V

REFCA

Reference Voltage for CA

V

TT

Termination Voltage

NC No Connection

RFU Reserved for Future Use

* Not used