User Guide

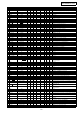

60

AVR-5805/AVC-A1XV

DM1000 (IC201) 1394 P.W.B.

74

65

66

67

68

69

70

71

72

73

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

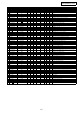

48

39

40

41

42

43

44

45

46

47

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

10

1

2

3

4

5

6

7

8

9

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

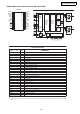

DM1000

IEEE1394 a/b

Interface Processor

128-pin QFP

SWMATRIX[6] *)

SWMATRIX[5] *)

SWMATRIX[4] *)

SWMATRIX[3] *)

AV2CLK

AV2CTRL[1] / NCS2

VSSIO

AV2CTRL[0] / A[20]

VDDIO

AV2DATA[7]

VSS

AV2DATA[6]

VDD

AV2DATA[5]

AV2DATA[4]

AV2DATA[3]

AV2DATA[2]

AV2DATA[1]

AV2DATA[0]

AV1CLK

AV1CTRL[1]

AV1CTRL[0]

VSS

VDD

AV1DATA[7]

VDDIO

AV1DATA[6]

VSSIO

AV1DATA[5]

AV1DATA[4]

AV1DATA[3]

AV1DATA[2]

AV1DATA[1]

AV1DATA[0]

NTEST1

NRESET

TEST2

PINT

NWE

NOE

NCS0

VSS

NCS1

VDD

A[10]

A[11]

VSSIO

VDDIO

A[12]

VSS

A[13]

VDD

A[14]

A[15]

A[16]

A[17]

*) SWMATRIX[0]

*) SWMATRIX[1]

*) SWMATRIX[2]

VSS

EXTCLK

VDD

VCOIN

VSSIO

PDOUT

VDDIO

*) SWMATRIX[8]

*) SWMATRIX[7]

113

104

105

106

107

108

109

110

111

112

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

103

A[0]

A[1]

VSSIO

VDDIO

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

A[8]

A[9]

D[13]

D[14]

D[15]

D[0]

D[1]

D[2]

D[3]

D[4]

D[5]

D[6]

D[7]

D[8]

D[9]

D[10]

VSS

D[11]

VDD

D[12]

VDDIO

VSSIO

PHYCLK

VSS

PHYD[7]

VDD

PHYD[6]

PHYD[5]

PHYD[4]

VSSIO

PHYD[3]

VDDIO

PHYD[2]

PHYD[1]

VSS

PHYD[0]

VDD

TEST3

LINKCLK

VSSIO

CTRL[1]

CTRL[0]

LREQ

VDDIO

VDDIO

LPS

VSSIO

LINKON

A[18]

A[19]

*) refer to chapter 4 fo r th e Sw itch-M atrix descrip tio n

Pin Assignment by Pin Number

Pi n Nam e Pi n Nam e Pi n Nam e Pi n Nam e

1 SWM ATRIX[6] *)

33 AV1DATA[1] 65 D[0] 97 A[4]

2 SWM ATRIX[5] *)

34 AV1DATA[7] 66 D[1] 98 A[5]

3 SWM ATRIX[4] *)

35 NTEST1 67 D[2] 99 A[6]

4 SWM ATRIX[3] *)

36 NRESET 68 D[3] 100 A[ 7]

5 AV2CLK

37 TEST2 69 D[4] 101 A[ 8]

6 AV2CTRL[1] / NCS[2]

38 PINT 70 D[5] 102 A[ 9]

7 VSSIO

39 VDDIO 71 D[6] 103 A[10]

8 AV2CTRL[0] / A[20]

40 LPS 72 D[7] 104 A[11]

9 VDDIO

41 VSSIO 73 D[8] 105 VSSIO

10 AV2DATA[7]

42 LINKON 7 4 D[9] 106 VDDIO

11 VSS

43 PHYCLK 75 D[10] 107 A[ 12]

12 AV2DATA[6]

44 VSS 76 VSS 108 VSS

13 VDD

45 PHYD[7] 77 D[11] 109 A[13]

14 AV2DATA[5]

46 VDD 78 VDD 11 0 VDD

15 AV2DATA[4]

47 PHYD[6] 79 D[12] 111 A[14]

16 AV2DATA[3]

48 PHYD[5] 80 VDDIO 11 2 A[15]

17 AV2DATA[2]

49 PHYD[4] 81 VSSIO 113 A[16]

18 AV2DATA[1]

50 VSSIO 82 D[13] 11 4 A[17]

19 AV2DATA[0]

51 PHYD[3] 83 D[14] 11 5 A[18]

20 AV1CLK

52 VDDIO 84 D[15] 11 6 A[19]

21 AV1CTRL[1]

53 PHYD[2] 85 NWE 117 SWM ATRIX[0] *)

22 VSS

54 PHYD[1] 86 NOE 11 8 VSS

23 AV1CTRL[0]

55 VSS 87 NCS[0] 119 EXTCLK

24 VDD

56 PHYD[0] 88 VSS 120 VDD

25 AV1DATA[7]

57 VDD 89 NCS[1] 121 VCOIN

26 VDDIO

58 TEST3 90 VDD 122 VSSIO

27 AV1DATA[6]

59 LINKCLK 91 A[ 0] 123 PDOUT

28 VSSIO

60 VSSIO 92 A[ 1] 124 VDDIO

29 AV1DATA[5]

61 CTRL[1] 93 VSSIO 125 SWMATRIX[1] *)

30 AV1DATA[4]

62 CTRL[0] 94 VDDIO 126 SWMATRIX[2] *)

31 AV1DATA[3]

63 LREQ 95 A[2] 127 SWMATRIX[8] *)

32 AV1DATA[2]

64 VDDIO 96 A[ 3] 128 SWMATRIX[7] *)