User Guide

12

12DN-C680

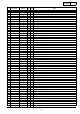

36 I/O(-INIT) -INIT O Pu FPGA(XCS05XL) control signal:-INIT

37 VCC VCC - - Power supply(+3.3V)

38 GND GND - - GND(0V)

39 I/O PDI5 I Pu Parallel port 'L':Forward search command input

40 I/O PDI6 I Pu Parallel port 'L':Reverse search command input

41 I/O PDI7 I Pu Parallel port 'L':Fader start command input

42 I/O PDI8 I Pu Parallel port(Reserved)

43 I/O PDI9 I Pu Parallel port(Reserved)

44 I/O PDI10 I Pu Parallel port(Reserved)

45 I/O -CLOSE O Pu Loading motor driver(BA6287) control signal 'L':Close

46 I/O -OPEN O Pu Loading motor driver(BA6287) control signal 'L':Open

47 I/O -LIMITSW+ I Pu Laser pickup position status signal 'L':pickup is most inside position

48 I/O,GCK4 -LDIN I Pu Loading status singal 'L':Close operation finished

49 GND GND - - GND(0V)

50 DONE DONE O Pu FPGA(XCS05XL) control signal:DONE

51 VCC VCC - - Power supply(+3.3V)

52 -PROGRAM -PGM I Pu FPGA(XCS05XL) control signal:-PROGRAM

53 I/O(D7) -LDOUT I Pu Loading status singal 'L':Open operation finished

54 I/O,GCK5 -JOG0 I Pu Jog dial status detect signal

55 I/O(D6) -JOG1 I Pu Jog dial status detect signal

56 I/O -SHTL0 I Pu Shuttle status detect signal

57 I/O(D5) -SHTL1 I Pu Shuttle status detect signal

58 I/O -SHTL2 I Pu Shuttle status detect signal

59 I/O -SHTL3 I Pu Shuttle status detect signal

60 I/O -TRSLC I Pu Select knob status signal

61 I/O(D4) -PUSH I Pu Select button(PUSH) status signal

62 I/O AMUTE O Pu Analog Audio control signal:Mute 'H':Mute

63 VCC VCC - - Power supply(+3.3V)

64 GND GND - - GND(0V)

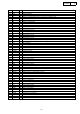

65 I/O(D3) DMUTE O Pu Digital Audio control signal:Mute 'H:Mute

66 I/O FSI0 O Pu X'tal(8.192MHz for FS converter unit) control signal:Enable 'L':Enable

67 I/O FSI1 O Pu X'tal(12.288MHz for FS converter unit) control signal:Enable 'L':Enable

68 I/O(D2) SEL0 O - Key matrix scan signal

69 I/O SEL1 O - Key matrix scan signal

70 I/O(D1) SEL2 O - Key matrix scan signal

71 I/O DYCON O Pu Serial Driver(HD26LS31) control signal:Enable 'H':Enable

72 I/O(D0,DIN) DIN I - FPGA(XCS05XL) control signal:DIN

73 I/O,GCK6(DOUT) I/O - - Not used. Open

74 CCLK CCLK I - FPGA(XCS05XL) control signal:CCLK

75 VCC VCC - - Power supply(+3.3V)

76 O,TDO O O - Not used. Open

77 GND GND - - GND(0V)

78 I/O -TRRST0 O Pd DIT(YM3437) and FS unit control signal:Reset 'L':Reset

79 I/O,GCK7 V/-W O Pd PLL circuit of Ext.sync.unit control signal

80 I/O(CS1) FSNOO O Pd Digital audio control signal:Data select 'L':DSP data 'H':FS unit data

81 I/O FSSEL O Pd FS unit control signal:FSSEL 'L':FS=32kHz 'H':FS=48kHz

82 I/O -FSIN I Pu FS unit status signal 'L':FS unit detected

83 I/O -SUBON O - Digital audio control signal:Subcode ON/OFF

84 I/O -SMIN I Pu Ext.sync.unit status signal 'L':Ext.sync.unit detected

85 I/O -CLKIN I Pu Ext.sync.unit status signal 'L':Video/word clock detected

86 I/O PITCH O Pd Not used. Open

87 I/O GSEL O - RF amprifier gain control signal

88 GND GND - - GND(0V)

89 VCC VCC - - Power supply(+3.3V)

90 I/O CKSEL O - Master clock(384FS) control signal 'L':Ext.sync.unit

Pin

No.

Port Name Symbol I/O Ext Note