Manual

Chromalox Instruments and Controls

A-51643 Rev. 6 10/06/03 6

3 Register and I/O Mapping

3.1 Unmapped and Reserved Registers

Reserved and NA registers will be read as zero with no exception error being generated. Thus, the host

can request data from multiple addresses with gaps between and still receive a valid response. Illegal and

undefined register address blocks will always generate an illegal data address exception.

Reserved and NA registers may be written without generating an exception, however the data is ignored

for these registers and no write takes place. Illegal and undefined register address blocks will always

generate an illegal data address exception.

3.2 Register Quantity Limitations

The number of registers that can be accessed in one query is limited to 50.

3.3 Discrete Input Assignments

The status of the four event inputs can be read as discrete inputs in Modbus format.

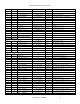

Table 3: Protocol

TM

Plus Discrete Input Address Map

Data Address

Hex Address

Description

Security

0

$0000

Event Input 1

0

1

$0001

Event Input 2

0

2

$0002

Event Input 3

0

3

$0003

Event Input 4

0

4 -- 7

$0004 -- $0007

Illegal, Reserved for future inputs

0

8 -- 65535

$0008 - $FFFF

Undefined, available for application assignment

0

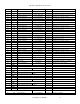

3.4 Discrete Output Assignments

The status of the four relay outputs can be read as discrete outputs in Modbus format. Writes to the

outputs are not supported, that is, the functions ―Write Single Output‖ (06) and ―Write Multiple Outputs‖

(15) are not implemented.