Datasheet

ENC424J600/624J600

DS39935C-page 6 2010 Microchip Technology Inc.

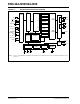

FIGURE 1-1: ENC424J600/624J600 BLOCK DIAGRAM

24 Kbytes

DMA and

Checksum

TX Control

RX Control

Arbiter

Flow Control

Host Interface

Control

Registers

25 MHz

Power-on

PHY

MII

Interface

MIIM

Interface

TPOUT+

TPOUT-

TPIN+

TPIN-

TX

RX

RBIAS

OSC1

OSC2

Control Logic

CS/CS

SI/RD/RW

SO

SCK/AL

INT

VCAP

CLKOUT

LEDA

LEDB

RX Filter

MAC

m3

m1

SRAM

Note 1: A<14:0>, AD15, WRL/B0SEL, WRH/B1SEL and PSPCFG<4:1> are available on 64-pin devices only. PSPCFG0 is available on 44-pin

devices only.

Reset

Oscillator

I/O

Interface

AD<15:0>

(1)

A<14:0>

(1)

Logic

Logic

Crypto Cores

Memory

Bus

Interface

SPIParallel Common

SPISEL

PSPCFGx

(1)

EN/B0SEL

(1)

WR/WRL/

WRH/

B1SEL

(1)

m0

m2

PLL

Voltage

Regulator