User manual

The 19-pin HDMI connectors include three differential data channels, one differential clock

channel five GND connections, a one-wire Consumer Electronics Control (CEC) bus, a two-wire

Display Data Channel (DDC) bus that is essentially an I2C bus, a Hot Plug Detect (HPD) signal,

a 5V signal capable of delivering up to 50mA, and one reserved (RES) pin. All non-power

signals are wired to the Zynq PL with the exception of RES.

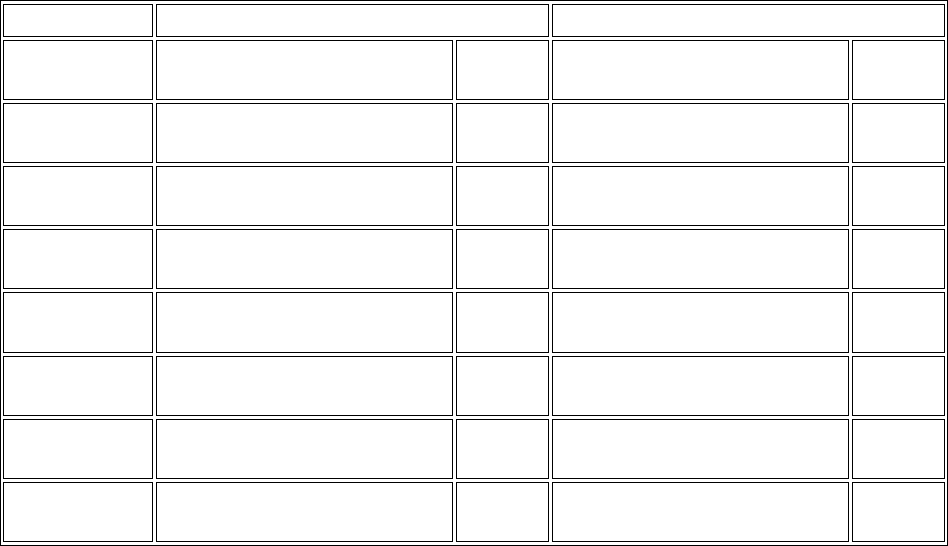

Pin/Signal J11 (source) J10 (sink)

Description

FPGA

pin

Description

FPGA

pin

D[2]_P,

D[2]_N

Data output J18, H18 Data input

N20,

P20

D[1]_P,

D[1]_N

Data output K19, J19 Data input

T20,

U20

D[0]_P,

D[0]_N

Data output

K17,

K18

Data input

V20,

W20

CLK_P,

CLK_N

Clock output

L16,

L17

Clock input

N18,

P19

CEC

Consumer Electronics

Control bidirectional

G15

Consumer Electronics

Control bidirectional

H17

SCL, SDA

DDC bidirectional

M17,

M18

DDC bidirectional

U14,

U15

HPD/HPA

Hot-plug detect input

(inverted)

R19 Hot-plug assert output T19

Table 10.1. HDMI pin description and assignment.

10.1 TMDS Signals

HDMI/DVI is a high-speed digital video stream interface using transition-minimized differential

signaling (TMDS). To make proper use of either of the HDMI ports, a standard-compliant

transmitter or receiver needs to be implemented in the Zynq PL. The implementation details are

outside the scope of this manual. Check out the vivado-library IP Core repository on the Digilent

github for ready-to-use reference IP.

10.2 Auxiliary signals

Whenever a sink is ready and wishes to announce its presence, it connects the 5V0 supply pin to

the HPD pin. On the Arty Z7, this is done by driving the Hot Plug Assert signal high. Note this

should only be done after a DDC channel slave has been implemented in the Zynq PL and is

ready to transmit display data.

The Display Data Channel, or DDC, is a collection of protocols that enable communication

between the display (sink) and graphics adapter (source). The DDC2B variant is based on I2C,