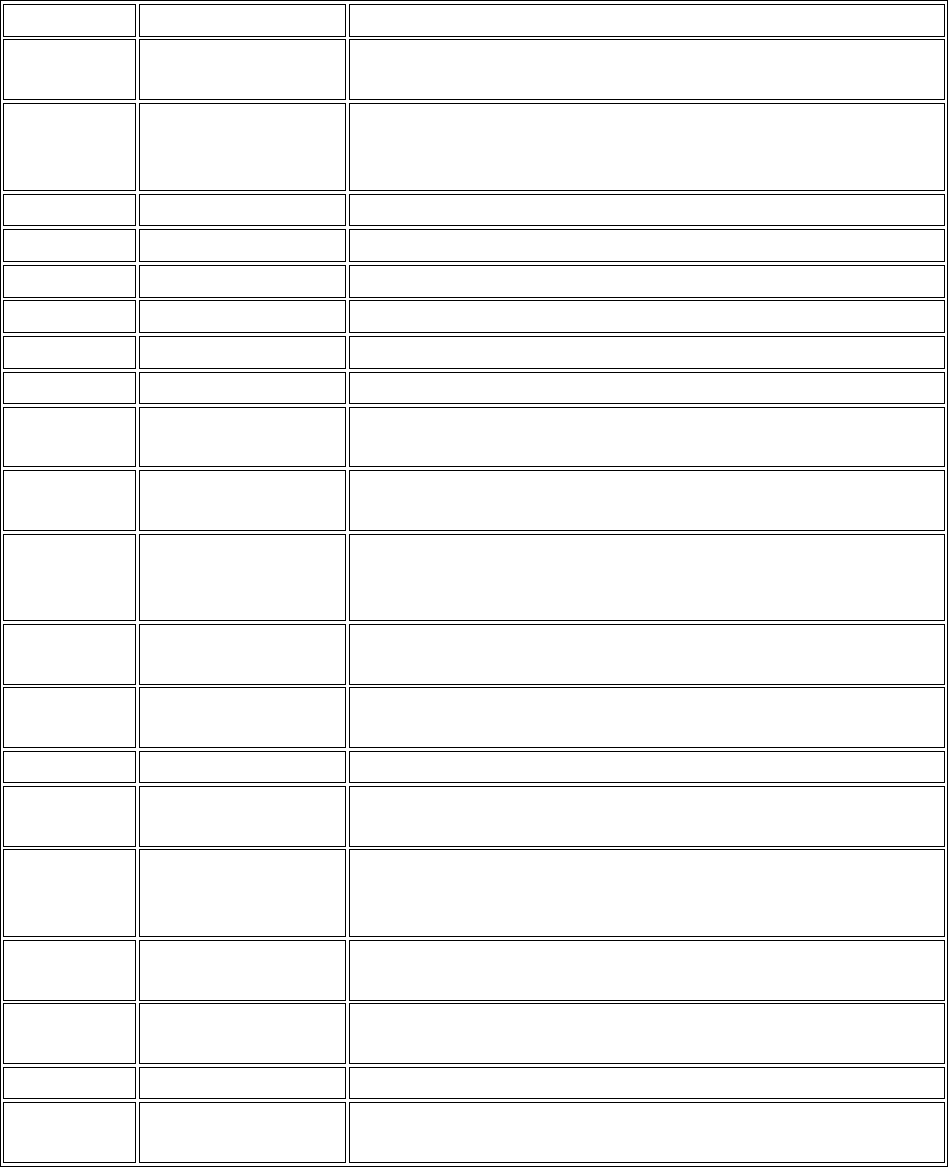

User manual

Pin Name Shield Function Arty Z7 Connection

IO0-IO13

General purpose I/O

pins

See Section titled “Shield Digital I/O”

IO26-IO41,

A (IO42)

Arty Z7-7020

General purpose I/O

pins

See Section titled “Shield Digital I/O”

SCL

I2C Clock See Section titled “Shield Digital I/O”

SDA

I2C Data See Section titled “Shield Digital I/O”

SCLK

SPI Clock See Section titled “Shield Digital I/O”

MOSI

SPI Data out See Section titled “Shield Digital I/O”

MISO

SPI Data in See Section titled “Shield Digital I/O”

SS

SPI Slave Select See Section titled “Shield Digital I/O”

A0-A5

Single-Ended

Analog Input

See Section titled “Shield Analog I/O”

A6-A11

Differential Analog

Input

See Section titled “Shield Analog I/O”

V_P, V_N

Dedicated

Differential Analog

Input

See Section titled “Shield Analog I/O”

XGND

XADC Analog

Ground

Connected to net used to drive the XADC ground reference

on the Zynq (VREFN)

XVREF

XADC Analog

Voltage Reference

Connected to 1.25 V, 25mA rail used to drive the XADC

voltage reference on the Zynq (VREFP)

N/C

Not Connected Not Connected

IOREF

Digital I/O Voltage

reference

Connected to the Arty Z7 3.3V Power Rail (See the “Power

Supplies” section)

RST

Reset to Shield

Connected to the red “SRST” button and MIO pin 12 of the

Zynq. When JP1 is shorted, it is also connected to the DTR

signal of the FTDI USB-UART bridge.

3V3

3.3V Power Rail

Connected to the Arty Z7 3.3V Power Rail (See the “Power

Supplies” section)

5V0

5.0V Power Rail

Connected to the Arty Z7 5.0V Power Rail (See the “Power

Supplies” section)

GND, G Ground Connected to the Ground plane of Arty Z7

VIN

Power Input

Connected in parallel with the external power supply

connector (J18).

Table 16.1. Shield Pin Descriptions.

16.1 Shield Digital I/O