User manual

Table Of Contents

- Zynq-7000 All Programmable SoC

- Table of Contents

- Ch. 1: Introduction

- Ch. 2: Signals, Interfaces, and Pins

- Ch. 3: Application Processing Unit

- Ch. 4: System Addresses

- Ch. 5: Interconnect

- Ch. 6: Boot and Configuration

- Ch. 7: Interrupts

- Ch. 8: Timers

- Ch. 9: DMA Controller

- Introduction

- Functional Description

- DMA Transfers on the AXI Interconnect

- AXI Transaction Considerations

- DMA Manager

- Multi-channel Data FIFO (MFIFO)

- Memory-to-Memory Transfers

- PL Peripheral AXI Transactions

- PL Peripheral Request Interface

- PL Peripheral - Length Managed by PL Peripheral

- PL Peripheral - Length Managed by DMAC

- Events and Interrupts

- Aborts

- Security

- IP Configuration Options

- Programming Guide for DMA Controller

- Programming Guide for DMA Engine

- Programming Restrictions

- System Functions

- I/O Interface

- Ch. 10: DDR Memory Controller

- Introduction

- AXI Memory Port Interface (DDRI)

- DDR Core and Transaction Scheduler (DDRC)

- DDRC Arbitration

- Controller PHY (DDRP)

- Initialization and Calibration

- DDR Clock Initialization

- DDR IOB Impedance Calibration

- DDR IOB Configuration

- DDR Controller Register Programming

- DRAM Reset and Initialization

- DRAM Input Impedance (ODT) Calibration

- DRAM Output Impedance (RON) Calibration

- DRAM Training

- Write Data Eye Adjustment

- Alternatives to Automatic DRAM Training

- DRAM Write Latency Restriction

- Register Overview

- Error Correction Code (ECC)

- Programming Model

- Ch. 11: Static Memory Controller

- Ch. 12: Quad-SPI Flash Controller

- Ch. 13: SD/SDIO Controller

- Ch. 14: General Purpose I/O (GPIO)

- Ch. 15: USB Host, Device, and OTG Controller

- Introduction

- Functional Description

- Programming Overview and Reference

- Device Mode Control

- Device Endpoint Data Structures

- Device Endpoint Packet Operational Model

- Device Endpoint Descriptor Reference

- Programming Guide for Device Controller

- Programming Guide for Device Endpoint Data Structures

- Host Mode Data Structures

- EHCI Implementation

- Host Data Structures Reference

- Programming Guide for Host Controller

- OTG Description and Reference

- System Functions

- I/O Interfaces

- Ch. 16: Gigabit Ethernet Controller

- Ch. 17: SPI Controller

- Ch. 18: CAN Controller

- Ch. 19: UART Controller

- Ch. 20: I2C Controller

- Ch. 21: Programmable Logic Description

- Ch. 22: Programmable Logic Design Guide

- Ch. 23: Programmable Logic Test and Debug

- Ch. 24: Power Management

- Ch. 25: Clocks

- Ch. 26: Reset System

- Ch. 27: JTAG and DAP Subsystem

- Ch. 28: System Test and Debug

- Ch. 29: On-Chip Memory (OCM)

- Ch. 30: XADC Interface

- Ch. 31: PCI Express

- Ch. 32: Device Secure Boot

- Appx. A: Additional Resources

- Appx. B: Register Details

- Overview

- Acronyms

- Module Summary

- AXI_HP Interface (AFI) (axi_hp)

- CAN Controller (can)

- DDR Memory Controller (ddrc)

- CoreSight Cross Trigger Interface (cti)

- Performance Monitor Unit (cortexa9_pmu)

- CoreSight Program Trace Macrocell (ptm)

- Debug Access Port (dap)

- CoreSight Embedded Trace Buffer (etb)

- PL Fabric Trace Monitor (ftm)

- CoreSight Trace Funnel (funnel)

- CoreSight Intstrumentation Trace Macrocell (itm)

- CoreSight Trace Packet Output (tpiu)

- Device Configuration Interface (devcfg)

- DMA Controller (dmac)

- Gigabit Ethernet Controller (GEM)

- General Purpose I/O (gpio)

- Interconnect QoS (qos301)

- NIC301 Address Region Control (nic301_addr_region_ctrl_registers)

- I2C Controller (IIC)

- L2 Cache (L2Cpl310)

- Application Processing Unit (mpcore)

- On-Chip Memory (ocm)

- Quad-SPI Flash Controller (qspi)

- SD Controller (sdio)

- System Level Control Registers (slcr)

- Static Memory Controller (pl353)

- SPI Controller (SPI)

- System Watchdog Timer (swdt)

- Triple Timer Counter (ttc)

- UART Controller (UART)

- USB Controller (usb)

Zynq-7000 AP SoC Technical Reference Manual www.xilinx.com 2

UG585 (v1.11) September 27, 2016

Notice of Disclaimer

The information disclosed to you hereunder (the “Materials”) is provided solely for the selection and use of Xilinx products. To the maximum

extent permitted by applicable law: (1) Materials are made available “AS IS” and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES

AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY,

NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including

negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with,

the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage

(including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such

damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct

any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce,

modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions

of Xilinx’s limited warranty, please refer to Xilinx’s Terms of Sale which can be viewed at http://www.xilinx.com/legal.htm#tos

; IP cores may be

subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be

fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in such

critical applications, please refer to Xilinx’s Terms of Sale which can be viewed at http://www.xilinx.com/legal.htm#tos

.

Automotive Applications Disclaimer

AUTOMOTIVE PRODUCTS (IDENTIFIED AS "XA" IN THE PART NUMBER) ARE NOT WARRANTED FOR USE IN THE DEPLOYMENT OF AIRBAGS

OR FOR USE IN APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE ("SAFETY APPLICATION") UNLESS THERE IS A SAFETY CONCEPT OR

REDUNDANCY FEATURE CONSISTENT WITH THE ISO 26262 AUTOMOTIVE SAFETY STANDARD ("SAFETY DESIGN"). CUSTOMER SHALL,

PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE PRODUCTS, THOROUGHLY TEST SUCH SYSTEMS FOR SAFETY

PURPOSES. USE OF PRODUCTS IN A SAFETY APPLICATION WITHOUT A SAFETY DESIGN IS FULLY AT THE RISK OF CUSTOMER, SUBJECT ONLY

TO APPLICABLE LAWS AND REGULATIONS GOVERNING LIMITATIONS ON PRODUCT LIABILITY.

© Copyright 2012-2016 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands

included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective

owners.

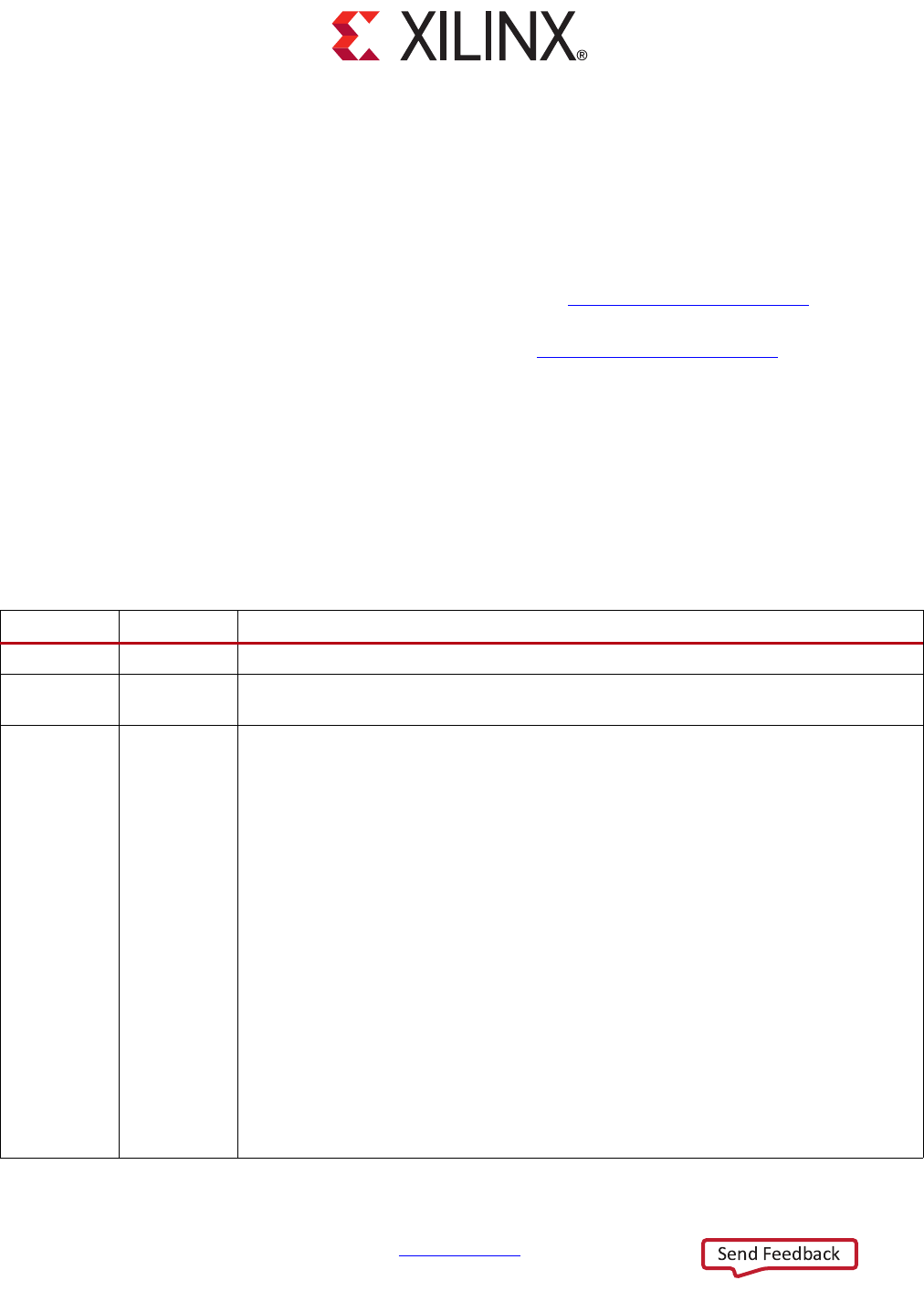

The following table shows the revision history for this document. Change bars indicate the latest revisions.

Date Version Revision

04/08/2012 1.0 Xilinx initial release.

06/25/2012 1.1 Removed Chapter 30, Board Design (now part of UG933, Zynq-7000 All Programmable

SoC PCB Design and Pin Planning Guide).

08/08/2012 1.2 Added information about the

7z010 CLG225 device and references to section

2.5.4 MIO-at-a-Glance Table throughout document.

Added section headings

1.1.1 Block Diagram and 1.1.2 Documentation Resources, added sections 1.1.3 Notices

and TrustZone Capabilities, and clarified PS MIO I/Os in Chapter 1. Updated Table 2-1.

Changed 2.4.2 MIO-EMIO Connections heading to 2.5.2 IOP Interface Connections and

clarified first paragraph. Updated Table 2-4. Added section 2.7.1 Clocks and Resets and

Table 2-7, and updated Table 2-13 PS MIO I/Os in Chapter 2. Added note under Branch

Prediction and Table 3-8 in Chapter 3. Updated Table 4-1 in Chapter 4. Added section

5.1.7 Read/Write Request Capability in Chapter 5. Updated

NAND Boot MIO pin

assignments and

Table 6-6 in Chapter 6. Updated section 7.1.5 CPU Interrupt Signal

Pass-through in Chapter 7. Added section heading 10.1.1 Features and added section

10.1.3 Notices in Chapter 10. Updated Parallel (SRAM/NOR) Interface features list and

added section 11.1.3 Notices in Chapter 11. Reorganized, clarified, and expanded

Chapter 12 to include programming models (added sections 12.1.4 Notices,

12.3 Programming Guide, and 12.5.2 MIO Programming). Added last note in section

13.3.4 Using ADMA in Chapter 13. Added Restrictions in Chapter 14. Clarified first

paragraph, added section 15.1.3 Notices, and clarified Figure 15-7 through

Figure 15-17 in Chapter 15. Added section 16.1.4 Notices in Chapter 16. Clarified

sections 17.2.5 SPI FIFOs, 17.2.6 SPI Clocks, and 17.2.7 SPI EMIO Considerations in

Chapter 17. Reorganized, clarified, and expanded Chapter 18 to include programming

models (added sections 18.1.4 Notices and 18.5.1 MIO Programming).