User manual

Table Of Contents

- Zynq-7000 All Programmable SoC

- Table of Contents

- Ch. 1: Introduction

- Ch. 2: Signals, Interfaces, and Pins

- Ch. 3: Application Processing Unit

- Ch. 4: System Addresses

- Ch. 5: Interconnect

- Ch. 6: Boot and Configuration

- Ch. 7: Interrupts

- Ch. 8: Timers

- Ch. 9: DMA Controller

- Introduction

- Functional Description

- DMA Transfers on the AXI Interconnect

- AXI Transaction Considerations

- DMA Manager

- Multi-channel Data FIFO (MFIFO)

- Memory-to-Memory Transfers

- PL Peripheral AXI Transactions

- PL Peripheral Request Interface

- PL Peripheral - Length Managed by PL Peripheral

- PL Peripheral - Length Managed by DMAC

- Events and Interrupts

- Aborts

- Security

- IP Configuration Options

- Programming Guide for DMA Controller

- Programming Guide for DMA Engine

- Programming Restrictions

- System Functions

- I/O Interface

- Ch. 10: DDR Memory Controller

- Introduction

- AXI Memory Port Interface (DDRI)

- DDR Core and Transaction Scheduler (DDRC)

- DDRC Arbitration

- Controller PHY (DDRP)

- Initialization and Calibration

- DDR Clock Initialization

- DDR IOB Impedance Calibration

- DDR IOB Configuration

- DDR Controller Register Programming

- DRAM Reset and Initialization

- DRAM Input Impedance (ODT) Calibration

- DRAM Output Impedance (RON) Calibration

- DRAM Training

- Write Data Eye Adjustment

- Alternatives to Automatic DRAM Training

- DRAM Write Latency Restriction

- Register Overview

- Error Correction Code (ECC)

- Programming Model

- Ch. 11: Static Memory Controller

- Ch. 12: Quad-SPI Flash Controller

- Ch. 13: SD/SDIO Controller

- Ch. 14: General Purpose I/O (GPIO)

- Ch. 15: USB Host, Device, and OTG Controller

- Introduction

- Functional Description

- Programming Overview and Reference

- Device Mode Control

- Device Endpoint Data Structures

- Device Endpoint Packet Operational Model

- Device Endpoint Descriptor Reference

- Programming Guide for Device Controller

- Programming Guide for Device Endpoint Data Structures

- Host Mode Data Structures

- EHCI Implementation

- Host Data Structures Reference

- Programming Guide for Host Controller

- OTG Description and Reference

- System Functions

- I/O Interfaces

- Ch. 16: Gigabit Ethernet Controller

- Ch. 17: SPI Controller

- Ch. 18: CAN Controller

- Ch. 19: UART Controller

- Ch. 20: I2C Controller

- Ch. 21: Programmable Logic Description

- Ch. 22: Programmable Logic Design Guide

- Ch. 23: Programmable Logic Test and Debug

- Ch. 24: Power Management

- Ch. 25: Clocks

- Ch. 26: Reset System

- Ch. 27: JTAG and DAP Subsystem

- Ch. 28: System Test and Debug

- Ch. 29: On-Chip Memory (OCM)

- Ch. 30: XADC Interface

- Ch. 31: PCI Express

- Ch. 32: Device Secure Boot

- Appx. A: Additional Resources

- Appx. B: Register Details

- Overview

- Acronyms

- Module Summary

- AXI_HP Interface (AFI) (axi_hp)

- CAN Controller (can)

- DDR Memory Controller (ddrc)

- CoreSight Cross Trigger Interface (cti)

- Performance Monitor Unit (cortexa9_pmu)

- CoreSight Program Trace Macrocell (ptm)

- Debug Access Port (dap)

- CoreSight Embedded Trace Buffer (etb)

- PL Fabric Trace Monitor (ftm)

- CoreSight Trace Funnel (funnel)

- CoreSight Intstrumentation Trace Macrocell (itm)

- CoreSight Trace Packet Output (tpiu)

- Device Configuration Interface (devcfg)

- DMA Controller (dmac)

- Gigabit Ethernet Controller (GEM)

- General Purpose I/O (gpio)

- Interconnect QoS (qos301)

- NIC301 Address Region Control (nic301_addr_region_ctrl_registers)

- I2C Controller (IIC)

- L2 Cache (L2Cpl310)

- Application Processing Unit (mpcore)

- On-Chip Memory (ocm)

- Quad-SPI Flash Controller (qspi)

- SD Controller (sdio)

- System Level Control Registers (slcr)

- Static Memory Controller (pl353)

- SPI Controller (SPI)

- System Watchdog Timer (swdt)

- Triple Timer Counter (ttc)

- UART Controller (UART)

- USB Controller (usb)

Zynq-7000 AP SoC Technical Reference Manual www.xilinx.com 5

UG585 (v1.11) September 27, 2016

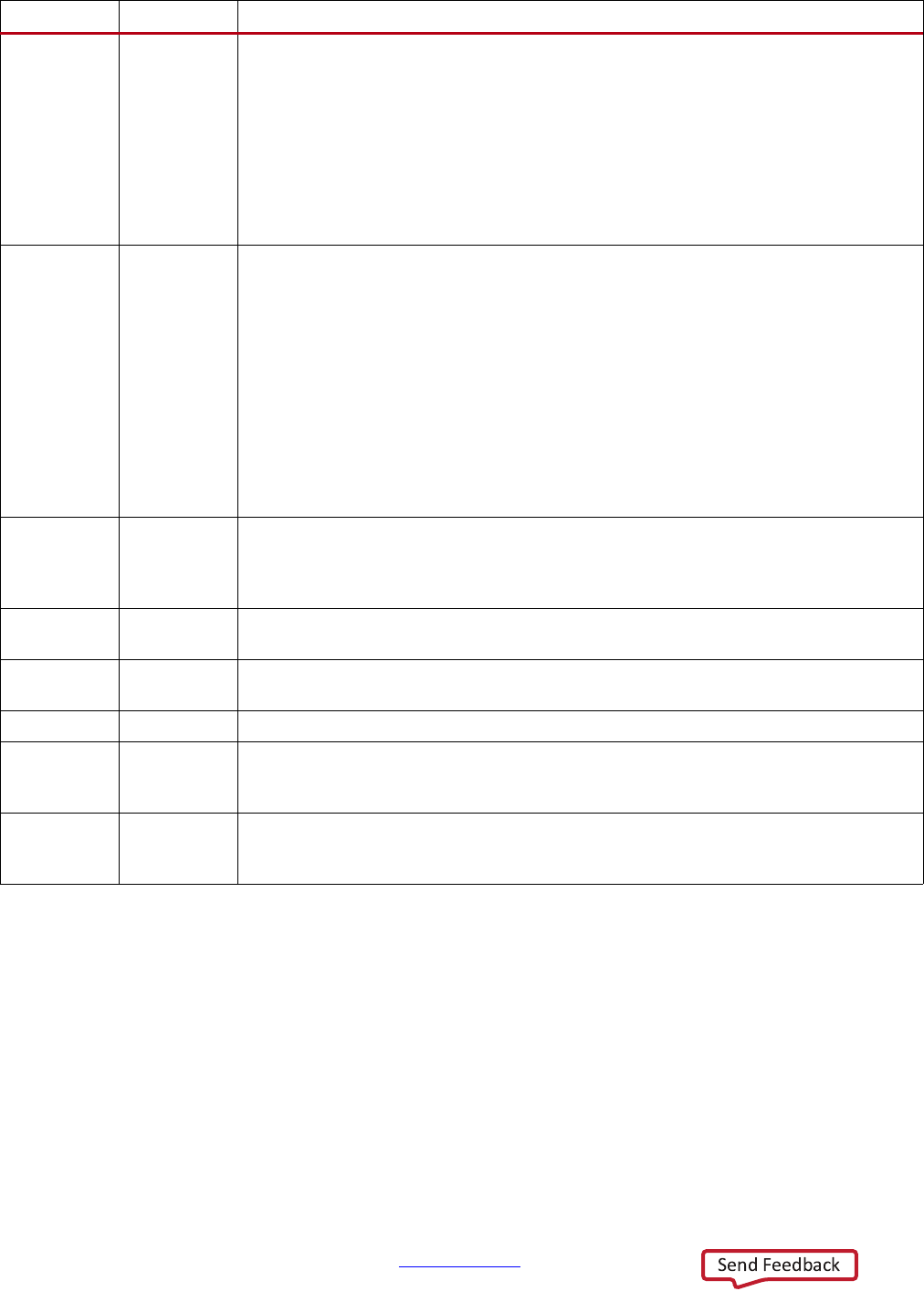

06/28/2013 1.6

(Cont’d)

Added section 31.5 Root Complex Use Case. Added FIPS standards and clarified section

32.1.2 Features, updated configuration file and secure boot process steps in

Figure 32-1, added boot time penalty to Power on Reset section, changed “Secure Boot”

heading to ”Secure FSBL Decryption”, changed “ROM code” to “OCM ROM Memory” in

Figure 32-2 and “ROM” to “OCM ROM” in Table 32-3, updated sections 32.2.7 Boot

Image and Bitstream Decryption and Authentication, 32.2.8 HMAC Signature,

32.2.9 AES Key Management, 32.3.1 Non-Secure Boot State, 32.3.4 Boot Partition

Search, and 32.3.7 Secure Boot Modes of Operation (deleted Table 32-4, “Non-secure

Boot Options”). Updated register database in sections B.3 Module Summary through

B.34 USB Controller (usb) in Appendix B.

02/11/2014 1.7 Added 7z015 device, updated device notices, and made minor clarifications throughout

document (denoted with change bars). Added section 3.10 Implementation-Defined

Configurations. Added sections 5.7 Loopback and 5.8 Exclusive AXI Accesses. Reworked

Chapter 6, Boot and Configuration. Added section 7.2.4 Interrupt Sensitivity, Targeting

and Handling. Added sections 8.4.6 Clock Input Option for SWDT and 8.5.6 Clock Input

Option for Counter/Timer. Updated section 10.7 Register Overview. Added section

11.7 NOR Flash Bandwidth. Added sections AXI Read Command Processing and

12.2.7 Supported Memory Read and Write Commands. Added section 16.1.4 Clock

Domains and reworked section 16.7 Known Issues (previously titled “Limitations”.

Updated section 21.1.2 PL Resources by Device Type and added section 21.3.4 GTP

Low-Power Serial Transceivers. Added Peripheral Clock Gating subsection. Updated

Table 26-1 and Table 26-4. Updated register database in sections B.3 Module Summary

through B.34 USB Controller (usb) in Appendix B.

09/16/2014 1.8 Added

position information for available device and package combinations for

the signals associated with each GT serial transceiver channel to sections

21.3.3 GTX Low-Power Serial Transceivers and 21.3.4 GTP Low-Power Serial

Transceivers.

09/19/2014 1.8.1 Removed erroneous banner from Chapter 21, Programmable Logic Description.

Corrected send feedback button clarity issue in footers.

11/17/2014 1.9 Added 7z035 device, updated device notices, and made minor clarifications throughout

document (denoted with change bars).

11/19/2014 1.9.1 Corrected document date.

02/23/2015 1.10 Added clarification on the

timing relationship between PL power up and the PS

POR reset signal to section 2.2 Power Pins and section 6.3.3 BootROM

Performance: PS_POR_B De-assertion Guidelines.

09/27/2016 1.11 Added 7z007s, 7z012s, and 7z014s single-core devices and updated the respective

device notices throughout document (denoted with change bars). Updated Figure 2-1,

Table 21-1, and Table 21-2. Updated device codes in Register PSS_IDCODE Details.

Date Version Revision