User manual

Table Of Contents

- Zynq-7000 All Programmable SoC

- Table of Contents

- Ch. 1: Introduction

- Ch. 2: Signals, Interfaces, and Pins

- Ch. 3: Application Processing Unit

- Ch. 4: System Addresses

- Ch. 5: Interconnect

- Ch. 6: Boot and Configuration

- Ch. 7: Interrupts

- Ch. 8: Timers

- Ch. 9: DMA Controller

- Introduction

- Functional Description

- DMA Transfers on the AXI Interconnect

- AXI Transaction Considerations

- DMA Manager

- Multi-channel Data FIFO (MFIFO)

- Memory-to-Memory Transfers

- PL Peripheral AXI Transactions

- PL Peripheral Request Interface

- PL Peripheral - Length Managed by PL Peripheral

- PL Peripheral - Length Managed by DMAC

- Events and Interrupts

- Aborts

- Security

- IP Configuration Options

- Programming Guide for DMA Controller

- Programming Guide for DMA Engine

- Programming Restrictions

- System Functions

- I/O Interface

- Ch. 10: DDR Memory Controller

- Introduction

- AXI Memory Port Interface (DDRI)

- DDR Core and Transaction Scheduler (DDRC)

- DDRC Arbitration

- Controller PHY (DDRP)

- Initialization and Calibration

- DDR Clock Initialization

- DDR IOB Impedance Calibration

- DDR IOB Configuration

- DDR Controller Register Programming

- DRAM Reset and Initialization

- DRAM Input Impedance (ODT) Calibration

- DRAM Output Impedance (RON) Calibration

- DRAM Training

- Write Data Eye Adjustment

- Alternatives to Automatic DRAM Training

- DRAM Write Latency Restriction

- Register Overview

- Error Correction Code (ECC)

- Programming Model

- Ch. 11: Static Memory Controller

- Ch. 12: Quad-SPI Flash Controller

- Ch. 13: SD/SDIO Controller

- Ch. 14: General Purpose I/O (GPIO)

- Ch. 15: USB Host, Device, and OTG Controller

- Introduction

- Functional Description

- Programming Overview and Reference

- Device Mode Control

- Device Endpoint Data Structures

- Device Endpoint Packet Operational Model

- Device Endpoint Descriptor Reference

- Programming Guide for Device Controller

- Programming Guide for Device Endpoint Data Structures

- Host Mode Data Structures

- EHCI Implementation

- Host Data Structures Reference

- Programming Guide for Host Controller

- OTG Description and Reference

- System Functions

- I/O Interfaces

- Ch. 16: Gigabit Ethernet Controller

- Ch. 17: SPI Controller

- Ch. 18: CAN Controller

- Ch. 19: UART Controller

- Ch. 20: I2C Controller

- Ch. 21: Programmable Logic Description

- Ch. 22: Programmable Logic Design Guide

- Ch. 23: Programmable Logic Test and Debug

- Ch. 24: Power Management

- Ch. 25: Clocks

- Ch. 26: Reset System

- Ch. 27: JTAG and DAP Subsystem

- Ch. 28: System Test and Debug

- Ch. 29: On-Chip Memory (OCM)

- Ch. 30: XADC Interface

- Ch. 31: PCI Express

- Ch. 32: Device Secure Boot

- Appx. A: Additional Resources

- Appx. B: Register Details

- Overview

- Acronyms

- Module Summary

- AXI_HP Interface (AFI) (axi_hp)

- CAN Controller (can)

- DDR Memory Controller (ddrc)

- CoreSight Cross Trigger Interface (cti)

- Performance Monitor Unit (cortexa9_pmu)

- CoreSight Program Trace Macrocell (ptm)

- Debug Access Port (dap)

- CoreSight Embedded Trace Buffer (etb)

- PL Fabric Trace Monitor (ftm)

- CoreSight Trace Funnel (funnel)

- CoreSight Intstrumentation Trace Macrocell (itm)

- CoreSight Trace Packet Output (tpiu)

- Device Configuration Interface (devcfg)

- DMA Controller (dmac)

- Gigabit Ethernet Controller (GEM)

- General Purpose I/O (gpio)

- Interconnect QoS (qos301)

- NIC301 Address Region Control (nic301_addr_region_ctrl_registers)

- I2C Controller (IIC)

- L2 Cache (L2Cpl310)

- Application Processing Unit (mpcore)

- On-Chip Memory (ocm)

- Quad-SPI Flash Controller (qspi)

- SD Controller (sdio)

- System Level Control Registers (slcr)

- Static Memory Controller (pl353)

- SPI Controller (SPI)

- System Watchdog Timer (swdt)

- Triple Timer Counter (ttc)

- UART Controller (UART)

- USB Controller (usb)

Zynq-7000 AP SoC Technical Reference Manual www.xilinx.com 657

UG585 (v1.11) September 27, 2016

Chapter 22: Programmable Logic Design Guide

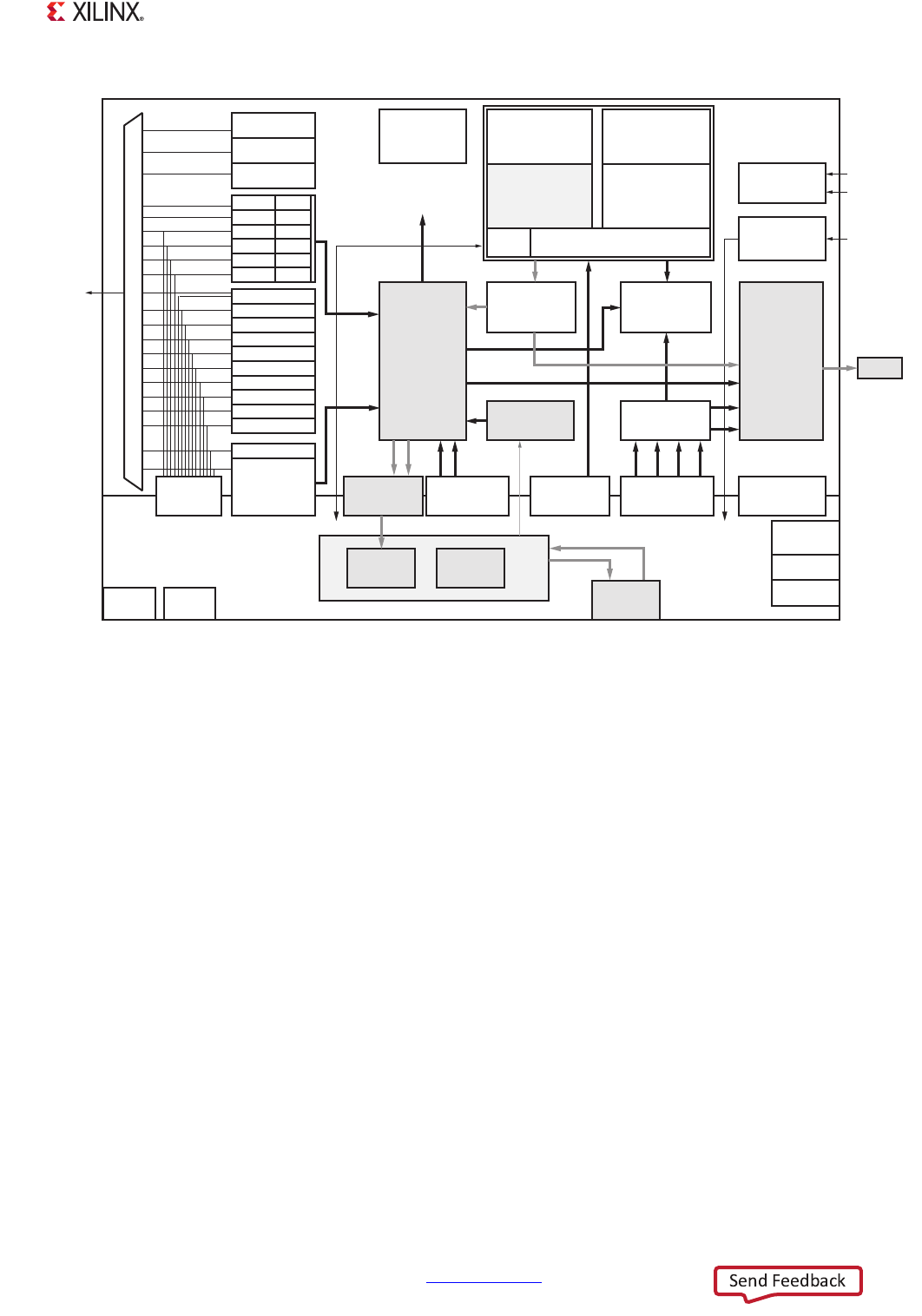

22.4.4 PL DMA via AXI High-Performance (HP) Interface

The high-performance (S_AXI_HP) PL interfaces provide high-bandwidth PL slave interfaces to OCM

and DDR memories. The AXI_HP ports are unable to access any other slaves. With four, 64-bit wide

interfaces, the AXI_HP provide the greatest aggregate interface bandwidth. The multiple interfaces

also save PL resources by reducing the need to a PL AXI interconnect. Each AXI_HP contains control

and data FIFOs to provide buffering of transactions for larger sets of bursts, making it ideal for

workloads such as video frame buffering in DDR. This additional logic and arbitration does result in

higher minimum latency than other interfaces.

The user IP logic residing in the PL will generally consist of a low-speed control interface and higher

performance burst interface, as shown in Figure 22-3. If control flow is orchestrated by the

Cortex-A9 CPU, the general purpose M_AXI_GP port can be used for tasks such as configuring the

memory addresses the User IP should access and transaction status. Transaction status can also be

conveyed via PL to PS interrupts. Higher performance devices connected to AXI_HP should be able to

issue multiple outstanding transactions to take advantage of the AXI_HP FIFOs.

The PL design complexity of multiple AXI interfaces along with the associated PL utilization are the

primary drawbacks of implementing a DMA engine in the PL for both S_AXI_HP and S_AXI_ACP

interfaces.

See Chapter 5, Interconnect for more information on the AXI_HP interface.

X-Ref Target - Figure 22-2

Figure 22-2: Example DMAC DMA Topology

IRQ

L2

Cache Memory

512 KB

DDR

Memory

Controller

16-bit

32-bit

16-bit w/ECC

DMA

8 channel

PCAP

Processor Config

Access Port

M_AXI_GP x 2

General Purpose

32-bit AXI Master

S_AXI_GP x 2

General Purpose

32-bit AXI Slave

S_AXI_HP x 4

AXI Data

32/64-bit Slave

SCU – Snoop Control Unit

Central

Interconnect

ARM A9

32 KB I-Cache

32 KB D-Cache

NEON

SP, DP FPU

128-bit Vector DSP

OCM

On Chip Memory

256 KB

S_AXI_ACP

AXI Coherent

64-bit Slave

Mem Switch

SLCR

System Level

Control

Registers

I/O Interface

Security

Config

XADC

16 ch ADC

Block RAM

User

IP

Control

Quad-SPI

1,2,4,8-bit

Parallel 8-bit

NOR/SRAM

NAND 8,16-bit

UART

UART

SPI

SPI

I2C

I2C

CAN

CAN

TTC/SWDT

PJTAG

Reset

CLK / PLL

ARM, I/O, DDR

PS_POR_B

PS_SRST_B

PS_CLK

DDR

CoreSight

Trace In

Trace Out

Cross Trigger

DAP

APB

Register Access

Processing

System (PS)

EMIO

USB

USB

GigE

GigE

SD

SD

DMA

DMA

DMA

DMA

DMA

DMA

GPIO x54, x64

MIO

Pins

NEON

SP, DP FPU

128-bit Vector DSP

ARM A9

32 KB I-Cache

32 KB D-Cache

UG585_c22_04_102414

Programmable

Logic (PL)

PCIe

GTX or

GTP

NOTE: GigaBit Transceiver and PCIe

functionality are not available in

all device versions and packages.