User manual

Table Of Contents

- Zynq-7000 All Programmable SoC

- Table of Contents

- Ch. 1: Introduction

- Ch. 2: Signals, Interfaces, and Pins

- Ch. 3: Application Processing Unit

- Ch. 4: System Addresses

- Ch. 5: Interconnect

- Ch. 6: Boot and Configuration

- Ch. 7: Interrupts

- Ch. 8: Timers

- Ch. 9: DMA Controller

- Introduction

- Functional Description

- DMA Transfers on the AXI Interconnect

- AXI Transaction Considerations

- DMA Manager

- Multi-channel Data FIFO (MFIFO)

- Memory-to-Memory Transfers

- PL Peripheral AXI Transactions

- PL Peripheral Request Interface

- PL Peripheral - Length Managed by PL Peripheral

- PL Peripheral - Length Managed by DMAC

- Events and Interrupts

- Aborts

- Security

- IP Configuration Options

- Programming Guide for DMA Controller

- Programming Guide for DMA Engine

- Programming Restrictions

- System Functions

- I/O Interface

- Ch. 10: DDR Memory Controller

- Introduction

- AXI Memory Port Interface (DDRI)

- DDR Core and Transaction Scheduler (DDRC)

- DDRC Arbitration

- Controller PHY (DDRP)

- Initialization and Calibration

- DDR Clock Initialization

- DDR IOB Impedance Calibration

- DDR IOB Configuration

- DDR Controller Register Programming

- DRAM Reset and Initialization

- DRAM Input Impedance (ODT) Calibration

- DRAM Output Impedance (RON) Calibration

- DRAM Training

- Write Data Eye Adjustment

- Alternatives to Automatic DRAM Training

- DRAM Write Latency Restriction

- Register Overview

- Error Correction Code (ECC)

- Programming Model

- Ch. 11: Static Memory Controller

- Ch. 12: Quad-SPI Flash Controller

- Ch. 13: SD/SDIO Controller

- Ch. 14: General Purpose I/O (GPIO)

- Ch. 15: USB Host, Device, and OTG Controller

- Introduction

- Functional Description

- Programming Overview and Reference

- Device Mode Control

- Device Endpoint Data Structures

- Device Endpoint Packet Operational Model

- Device Endpoint Descriptor Reference

- Programming Guide for Device Controller

- Programming Guide for Device Endpoint Data Structures

- Host Mode Data Structures

- EHCI Implementation

- Host Data Structures Reference

- Programming Guide for Host Controller

- OTG Description and Reference

- System Functions

- I/O Interfaces

- Ch. 16: Gigabit Ethernet Controller

- Ch. 17: SPI Controller

- Ch. 18: CAN Controller

- Ch. 19: UART Controller

- Ch. 20: I2C Controller

- Ch. 21: Programmable Logic Description

- Ch. 22: Programmable Logic Design Guide

- Ch. 23: Programmable Logic Test and Debug

- Ch. 24: Power Management

- Ch. 25: Clocks

- Ch. 26: Reset System

- Ch. 27: JTAG and DAP Subsystem

- Ch. 28: System Test and Debug

- Ch. 29: On-Chip Memory (OCM)

- Ch. 30: XADC Interface

- Ch. 31: PCI Express

- Ch. 32: Device Secure Boot

- Appx. A: Additional Resources

- Appx. B: Register Details

- Overview

- Acronyms

- Module Summary

- AXI_HP Interface (AFI) (axi_hp)

- CAN Controller (can)

- DDR Memory Controller (ddrc)

- CoreSight Cross Trigger Interface (cti)

- Performance Monitor Unit (cortexa9_pmu)

- CoreSight Program Trace Macrocell (ptm)

- Debug Access Port (dap)

- CoreSight Embedded Trace Buffer (etb)

- PL Fabric Trace Monitor (ftm)

- CoreSight Trace Funnel (funnel)

- CoreSight Intstrumentation Trace Macrocell (itm)

- CoreSight Trace Packet Output (tpiu)

- Device Configuration Interface (devcfg)

- DMA Controller (dmac)

- Gigabit Ethernet Controller (GEM)

- General Purpose I/O (gpio)

- Interconnect QoS (qos301)

- NIC301 Address Region Control (nic301_addr_region_ctrl_registers)

- I2C Controller (IIC)

- L2 Cache (L2Cpl310)

- Application Processing Unit (mpcore)

- On-Chip Memory (ocm)

- Quad-SPI Flash Controller (qspi)

- SD Controller (sdio)

- System Level Control Registers (slcr)

- Static Memory Controller (pl353)

- SPI Controller (SPI)

- System Watchdog Timer (swdt)

- Triple Timer Counter (ttc)

- UART Controller (UART)

- USB Controller (usb)

Zynq-7000 AP SoC Technical Reference Manual www.xilinx.com 714

UG585 (v1.11) September 27, 2016

Chapter 27: JTAG and DAP Subsystem

most CPU power. Based on that, the user could decide to either perform software optimization or

offload the process to the PL.

27.3 I/O Signals

In cascaded JTAG mode, only PL_TDO/TMS/TCK/TDI at the PL side are meaningful to users. Through

them, users can access both the ARM DAP and Xilinx TAP.

In independent JTAG mode, users can only access the Xilinx TAP, through PL_TDO/TMS/TCK/TDI. To

access the ARM DAP, users must use PJTAG signals, as shown in Table 27-1. There are two choices to

route PJTAG signals to chip pinouts: via EMIO to the PL SelectIO, or via MIO.

The MIO pins and any restrictions based on device version are shown in the MIO table in section

2.5.4 MIO-at-a-Glance Table.

The TPIU output, as shown at the bottom of Figure 27-3, can be routed to either EMIO or MIO (but

not both). The TPIU signals are listed in section 28.3 I/O Signals.

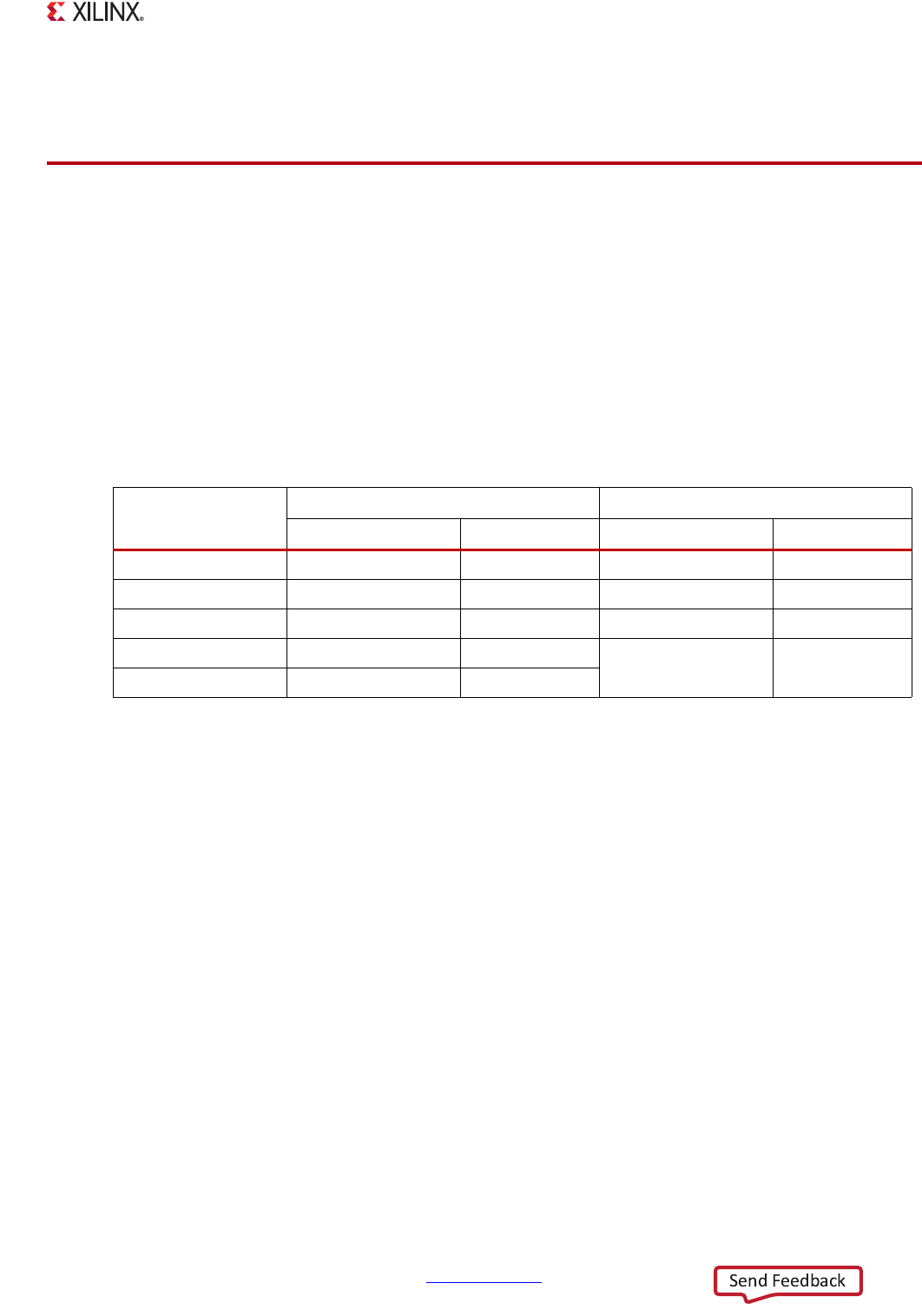

Table 27-1: PJTAG Signals

Signal Name

via EMIO via MIO

Signal I/O Pin I/O

TCK EMIOPJTAGTCK I MIO 12, 24, 36 or 48 I

TMS EMIOPJTAGTMS I MIO 13, 25, 37 or 49 I

TDI EMIOPJTAGTDI I MIO 10, 22, 34 or 46 I

TDO EMIOPJTAGTDO O

MIO 11, 23, 35 or 47 O

TDO 3-state EMIOPJTAGTDTN O