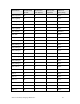

Instruction Manual

Instruction Hexadecimal

Opcode

Instruction

Size (Bytes)

CPU Cycles

Required

Affect on

Carry Flag

POP [3][offset] DB 2 7 None

POP [0][TOS] DC 1 6 None

POP [1][TOS] DD 1 6 None

POP [2][TOS] DE 1 6 None

POP [3][TOS] DF 1 6 None

POP FLAGS E0 1 4 Modified

POP RSP E2 1 4 None

POP DSP E3 1 4 None

POP [DSP][-8] F8 1 5 None

POP [DSP][-7] F9 1 5 None

POP [DSP][-6] FA 1 5 None

POP [DSP][-5] FB 1 5 None

POP [DSP][-4] FC 1 5 None

POP [DSP][-3] FD 1 5 None

POP [DSP][-2] FE 1 5 None

POP [DSP][-1] FF 1 5 None

POP address F7 3 7 None

POP !8 C8 1 4 None

POP !9 C9 1 4 None

POP !10 CA 1 4 None

POP !11 CB 1 4 None

POP !12 CC 1 4 None

POP !13 CD 1 4 None

POP !14 CE 1 4 None

Neuron Assembly Language Reference 97