Specifications

Chapter 2 – Hardware Resources

14 PL 3120/PL 3150/PL 3170 Power Line Smart Transceiver Data Boo

k

A processor instruction cycle is three system clock cycles, or six input clock (XIN) cycles. Most instructions take

between one and seven processor instruction cycles. At an input clock rate of 10MHz, instruction times vary between

0.6 μs and 4.2 μs. Execution time scales inversely with the input clock rate. The formula for instruction time is:

(Instruction Time) = (# Cycles) x 6 / (Input Clock)

Tables 2.3, 2.4, and 2.5 list the processor instructions, their timings (in cycles) and sizes (in bytes). This is provided for

purposes of calculating the execution time and size of code sequences. All programming of the PL Smart Transceiver is

typically done with Neuron C using the NodeBuilder development tool or the Mini EVK Evaluation Kit. The Neuron C

compiler can optionally produce an assembly listing, and examining this listing can help the programmer to optimize the

Neuron C source code.

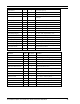

Table 2.3 Program Control Instructions

Mnemonic Cycles

Size

(bytes) Description Comments

NOP 1 1 No operation

SBR 1 1 Short unconditional branch Offset 0 to 15

BR/BRC/BRN

C

2 2 Branch, branch on (not) carry Offset -128 to +127

SBRZ/SBRNZ 3 1 Short branch on TOS (not) zero Offset 0 to 15. Drops TOS

BRF 4 3 Unconditional branch far Absolute address

BRZ/BRNZ 4 2 Branch on TOS (not) zero Offset -128 to +127. Drops TOS

RET 4 1 Return from subroutine Drops two bytes from return stack

BRNEQ 4/6 3 Branch if TOS not equal

(taken/not taken)

Offset -128 to +127. Drops TOS if

equal

DBRNZ 5 2 Decrement [RSP] and branch if

not zero

Offset -128 to +127. If not taken,

drops one byte from return stack

CALLR 5 2 Call subroutine relative Offset -128 to +127. Pushes two

bytes to return stack

CALL 6 2 Call subroutine Address in low 8KB. Pushes two

bytes to return stack

CALLF 7 3 Call subroutine far Absolute address. Pushes two

bytes to return stack

Table 2.4 Memory/Stack Instructions

Mnemonic Cycles Size (bytes) Comments / Effective Address (EA)

PUSH TOS 3 1 Increment DSP, duplicate TOS into NEXT

DROP TOS 3 1 Move NEXT to TOS, decrement DSP

DROP_R TOS 6 1 Move NEXT to TOS, decrement DSP, return from

call

PUSH (NEXT, DSP, RSP,

FLAGS)

4 1 Push processor register

POP (DSP, RSP, FLAGS) 4 1 Pop processor register

DROP NEXT 2 1 Decrement DSP

DROP_R NEXT 5 1 Decrement DSP and return from call