Specifications

PL 3120/PL 3150/PL 3170 Power Line Smart Transceiver Data Book 17

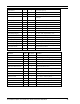

2.5KB Reserved

Space

42KB of Memory

Space Available

to the User

E7FF

4000

Internal

16KB Neuron

Firmware and

Reserved Space

3FFF

FFFF

F200

F1FF

0.5KB EEPROM

F000

EFFF

2KB RAM

E800

0000

1KB Reserved Space For

Memory Mapped I/O

FBFF

FC00

External

1KB Reserved Space For

Memory Mapped I/O

Unavailable

FBFF

24KB Neuron Firmware

(ROM)

5FFF

FFFF

FC00

EFFF

3KB EEPROM

F000

2KB RAM

E800

0000

Internal

Unavailable

1KB EEPROM

8000

83FF

Figure 2.5 PL 3150 Smart Transceiver Memory Map

Figure 2.6 PL 3120/PL 3170 Smart Transceiver Memory

Map

EEPROM

All three versions of the PL Smart Transceiver have internal EEPROM containing:

• Network configuration and addressing information.

• Unique 48-bit Neuron ID.

• Optional user-written application code and data tables.

All but 8 bytes of the EEPROM can be written under program control using an on-chip charge pump to generate the

required programming voltage. The charge pump operation is transparent to the user. The remaining 8 bytes are written

during manufacture, and contain a unique 48-bit identifier for each part called the Neuron ID, plus 16 bits for the chip

manufacturer’s device code. Each byte in the EEPROM region can be written up to 10,000 times. For all PL Smart

Transceivers, the EEPROM stores the installation-specific information such as network addresses and communications

parameters. For the PL 3120 and PL 3170 Smart Transceivers, the EEPROM also stores the application program

generated by the NodeBuilder or Mini EVK tool. The application code for the PL 3150 Smart Transceiver can be stored

either on-chip in the EEPROM memory or off-chip in external memory depending on the size of the application code.

See Table 2.6 for available EEPROM space.

For all write operations to the internal EEPROM, the Neuron firmware automatically compares the value in the

EEPROM location with the value to be written. If the two are the same, the write operation is not performed. This

prevents unnecessary write cycles to the EEPROM, and reduces the average EEPROM write cycle latency.