Solid State Drive Technology Differences between SLC, MLC and TLC NAND

Technical white paper | Solid State Drive Technology

3

Table 1. Write endurance

SLC MLC TLC

Bits per cell 1 2 3

P/E Cycles 100,000 3,000 1,000

Read Time 25us 50us ~75us

Program Time 200-300us 600-900us ~900-1350us

Erase Time 1.5-2ms 3ms ~4.5ms

SLC NAND flash typically rates endurance at about 100K cycles. MLC NAND flash is typically rated about 3K-5K cycles. TLC

NAND flash is typically rated about 1K-3K cycles. Fewer available PE cycles make it important that TLC maintain low write

amplification, because high write amplification will more quickly use up PE cycles.

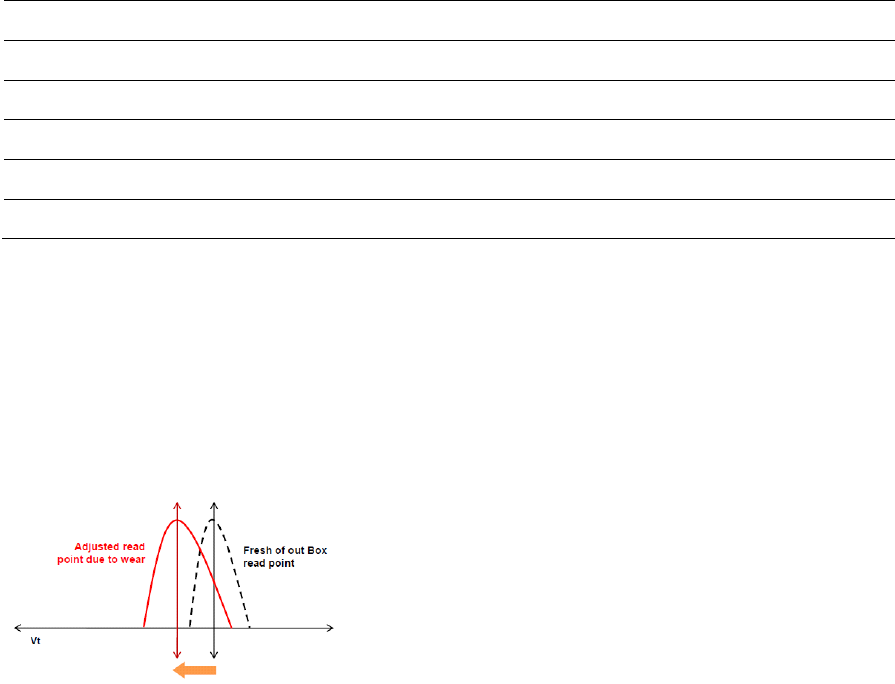

Wear leveling algorithms and write amplification are never perfect. Providing a specific number for endurance is very

difficult because every drive behaves differently and user workload varies. DPS (digital signal processing) solutions can help

with lower endurance NANDs. Every time you program or erase the cell, you degrade it, and the DSP reads the voltage

change and adapts to it. While a DSP won’t make the NAND last indefinitely, it does prevent stress to the NAND by allowing it

to last for more P/E cycles. If it can extend NAND life, it helps suppliers use smaller process nodes and possibly more bits

per cell.

As higher density devices come online, a new coding technique known as Adaptive Endurance Code (AEC) can help increase

the number of program/erase cycles that a flash device can endure. Data-dependant wear implies that flash device lifetime

can significantly be increased by converting data into bit patterns prior to programming, which cause minimal wear. AEC can

be adapted to data compressibility to maximize endurance gains with low system overhead cost.

Block copy time is the largest limiting factor for random write performance. As block copy times increases, random

performance decreases.

Key factors that impact NAND Flash random write performance are as follows:

• Number of pages per blocks

• Increase of tPROG

• Increase in I/O transfer time