Datasheet

C515C

Data Sheet 53 2003-02

Fail Save Mechanisms

The C515C offers two on-chip peripherals which monitor the program flow and ensure

an automatic “fail-safe” reaction for cases where the controller’s hardware fails or the

software hangs up:

• A programmable watchdog timer (WDT) with variable time-out period from

512 microseconds up to approx. 1.1 seconds at 6 MHz.

• An oscillator watchdog (OWD) which monitors the on-chip oscillator and forces the

microcontroller into reset state in case the on-chip oscillator fails; it also provides the

clock for a fast internal reset after power-on.

Programmable Watchdog Timer

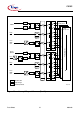

The watchdog timer in the C515C is a 15-bit timer, which is incremented by a count rate

of

f

OSC

/12 up to f

OSC

/192. For programming of the watchdog timer overflow rate, the

upper 7 bit of the watchdog timer can be written. Figure 23 shows the block diagram of

the watchdog timer unit.

Figure 23 Block Diagram of the Programmable Watchdog Timer

The watchdog timer can be started by software (bit SWDT) or by hardware through pin

PE

/SWD, but it cannot be stopped during active mode of the C515C. If the software fails

to refresh the running watchdog timer an internal reset will be initiated on watchdog timer

overflow. For refreshing of the watchdog timer the content of the SFR WDTREL is

transferred to the upper 7-bit of the watchdog timer. The refresh sequence consists of

MCB02755

Control Logic

PE/SWD

External HW Power-Down

WDT Reset Request

14 8

WDTH

WDTREL (86 )

07

6

IEN1 (B8 )

IEN0 (A8 )

H

H

07

WDTL

IP0 (A9 )

H

WDT

SWDT -

-

-

-

-

-

-

-

-

-

-

--

-

H

External HW Reset

-------WDTS

WDTPSEL

÷16

/6

OSC

f ÷2