Intel Pentium M Processor on 90nm Process with 2-MB L2 Cache Datasheet

Datasheet 55

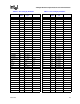

Package Mechanical Specifications and Pin Information

Figure 4-7. The Coordinates of the Processor Pins as Viewed from the Top of the Package

1234567891011121314151617181920212223242526

IGNNE# IERR# VSS SLP# DBR# VSS BPM[2]# PRDY# VSS TDO TCK VSS

ITP_CLK

[1]

ITP_CLK

[0]

VSS

THER

MDC

D[0]# VSS D[6]# D[2]# VSS D[4]# D[1]# VSS

VSS SMI# INIT# VSS DPSLP#

BPM

[1]#

VSS PREQ# RESET# VSS TRST# BCLK1 BCLK0 VSS

PROC

HOT #

THER

MDA

VSS D[7]# D[3]# VSS D[13]# D[9]# VSS D[5]#

VSS

A20M# RSVD

VSS TEST1

STP

CLK#

VSS

BPM

[0]#

BPM

[3]#

VSS TMS TDI VSS BSEL[1] VSS BSEL[0]

THERM

TRIP#

VSS DPWR# D[8]# VSS

DSTBP

[0]#

DSTBN

[0]#

VSS D[15]# D[12]#

LINT0 VSS FERR# LINT1 VSS VCC VSS VCC VSS VCCP VSS VCCP VSS VCCP VSS VCCP VSS VCC VSS VCC VSS VCC VSS D[10]#

DINV

[0]#

VSS

PSI# VID[0]

PWR

GOOD

VCC VSS VCC VSS VCC VSS VCCP VSS VCCP VSS VCCP VSS VCC VSS VCC VSS VCC

VSS

D[14]# D[11]# VSS RSVD

VSS VID[1] VID[2] VSS VSS VCC VSS VCC VSS VCCP VSS VCCP VSS VCCP VSS VCCP VSS VCC VSS VCC VSS

VCC TEST2

VSS D[21]# VCCA[0]

RSVD VSS VID[3] VID[4] VCC VSS VCC VSS VSS D[22]# D[17]# VSS

RS[0]# DRDY# VSS VID[5] VSS VCC VSS VCC D[16]# D[20]# VSS D[29]#

VSS LOCK# BPRI# VSS VCC VSS VCC VSS D[23]# VSS D[25]#

DINV

[1]#

RS[1]# VSS HIT# HITM# VSS VCCP VSS VCC VSS

DSTBN

[1]#

D[31]# VSS

BNR# RS[2]# VSS

DEFER#

VCCP

VSS

VCCP VSS D[18]#

DSTBP

[1]#

VSS D[26]#

DBSY# TRDY# VSS VSS VCCP VSS VCCP D[24]# VSS D[28]# D[19]#

VCCA[2] ADS# VSS BR0# VCCP VSS VCCP VSS VSS D[27]# D[30]# VSS

REQ

[3]#

VSS

REQ

[1]#

A[3]# VSS VCCP VSS VCCP

VCCQ[0]

VSS

COMP

[0]

COMP

[1]

VSS

REQ

[0]#

A[6]# VSS VCCP

VSS VCCP

VSS D[39]# D[37]# VSS D[38]#

REQ

[4]#

REQ

[2]#

VSS A[9]# VSS VCCP VSS VCCP VSS

DINV

[2]#

D[34]# VSS

A[13]# VSS

ADSTB

[0]#

A[4]# VCC VSS VCCP VSS D[35]# VSS D[43]# D[41]#

VSS A[7]# A[5]# VSS VSS VCC VSS VCC D[36]# D[42]# VSS D[44]#

A[8]# A[10]# VSS VCCQ[1] VCC VSS

VCC

VSS VSS

DSTBP

[2]#

DSTBN

[2]#

VSS

A[12]# VSS A[15]# VSS VCC VSS VCC D[45]# VSS D[47]# D[32]#

VSS A[16]# A[14]# VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC

VSS

VCC

VSS

D[40]# D[33]# VSS D[46]#

COMP

[3]

COMP

[2]

VSS

A[24]#

VSS

VCC VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC VSS D[50]# D[48]# VSS

RSVD

VSS A[20]# A[18]# VSS A[25]# A[19]# VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC D[51]# VSS D[52]# D[49]# VSS D[53]# VCCA[3]

VSS A[23]# A[21]# VSS

A[26]#

A[28]# VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC VSS

DINV

[3]#

D[60]# VSS D[54]# D[57]# VSS GTLREF

A[30]# A[27]# VSS A[22]#

ADSTB

[1]#

VSS

VCC

SENSE

VSS VCC VSS VCC VSS VCC VSS VCC

VSS

VCC VSS VCC VSS D[59]# D[55]# VSS

DSTBN

[3]#

DSTBP

[3]#

VSS

A[31]#

A[31]# VSS A[29]# A[17]# VSS

VSS

SENSE

RSVD VCC VSS VCC VSS

VCC

vss

VCC VSS

VCC

VSS VCC VSS D[58]# VSS D[62]# D[56]# VSS D[61]# D[63]#

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

VSS

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

1234567891011121314151617181920212223242526

VSS VCC Other

VSS

A[11]#

VSS

TOP VIEW

VCCA[1]

Pin B2 is depopulated on the Micro-FCPGA package

RSVD