Specification Update

Table Of Contents

Summary Tables of Changes

Specification Update 23

Steppings

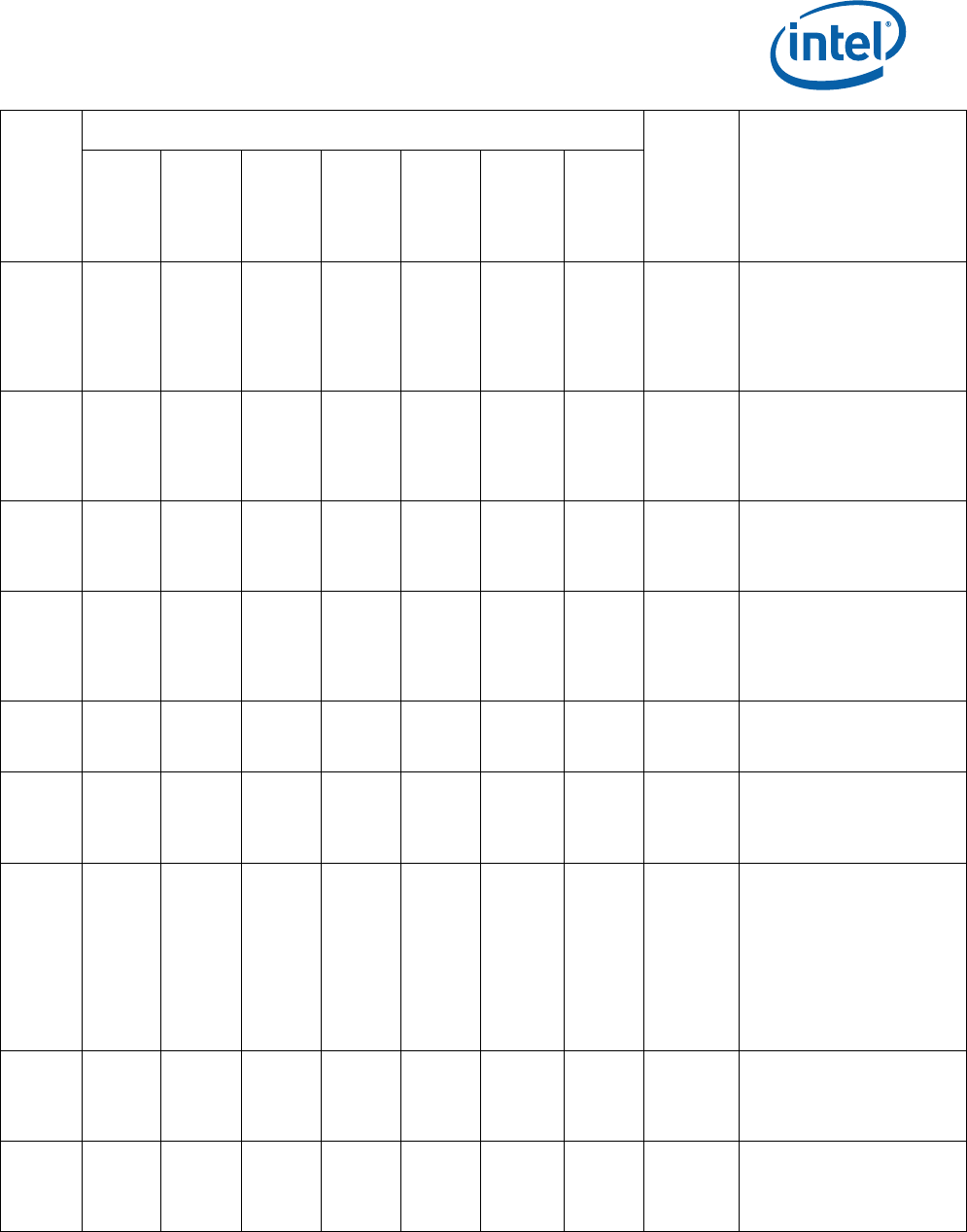

NO.

B-1 CPU

Signature

= 06D6h

C-0 CPU

Signature

= 06D8h

B-1 CPU

Signature

= 0695h

C-0 CPU

Signature

= 06E8h

D-0 CPU

Signature

= 06ECh

B-2 CPU

Signature

= 06F6h

A-1 CPU

Signature

= 10661h

Plans

ERRATA

W105 X X No Fix

(E)CX May Get Incorrectly

Updated When Performing

Fast String REP MOVS or

Fast String REP STOS

With Large Data

Structures

W106 X X No Fix

Performance Monitoring

Events for Retired Loads

(CBH) and Instructions

Retired (C0H) May Not Be

Accurate

W107 X X No Fix

Upper 32 bits of 'From'

Address Reported through

BTMs or BTSs May be

Incorrect

W108 X X No Fix

Unsynchronized Cross-

Modifying Code

Operations Can Cause

unexpected Instruction

Execution Results

W109 X X No Fix

Split Locked Stores May

not Trigger the Monitoring

Hardware

W110 X X Plan Fix

REP CMPS/SCAS

Operations May Terminate

Early in 64-bit Mode when

RCX >= 0X100000000

W111 X X No Fix

FXSAVE/FXRSTOR

Instructions which Store

to the End of the Segment

and Cause a Wrap to a

Misaligned Base Address

(Alignment <= 0x10h)

May Cause FPU

Instruction or Operand

Pointer Corruption

W112 X X No Fix

PREFETCHh Instruction

Execution under Some

Conditions May Lead to

Processor Livelock

W113 X X No Fix

PREFETCHh Instructions

May Not be Executed

when Alignment Check

(AC) is Enabled