Specification Update

Table Of Contents

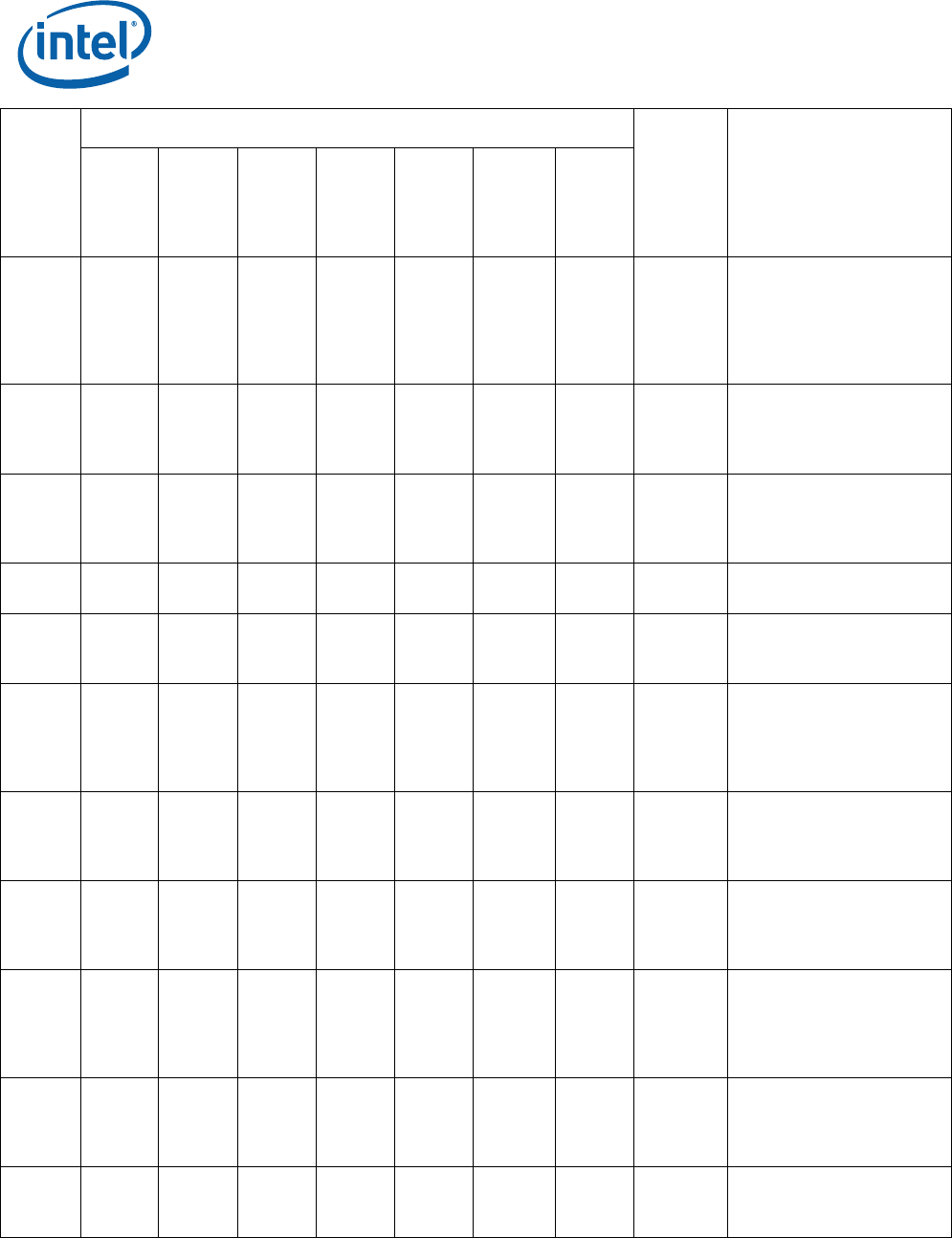

Summary Tables of Changes

24 Specification Update

Steppings

NO.

B-1 CPU

Signature

= 06D6h

C-0 CPU

Signature

= 06D8h

B-1 CPU

Signature

= 0695h

C-0 CPU

Signature

= 06E8h

D-0 CPU

Signature

= 06ECh

B-2 CPU

Signature

= 06F6h

A-1 CPU

Signature

= 10661h

Plans

ERRATA

W114 X X No Fix

Upper 32 Bits of the FPU

Data (Operand) Pointer in

the FXSAVE Memory

Image May Be

Unexpectedly All 1's after

FXSAVE

W115 X X No Fix

Performance Monitor

IDLE_DURING_DIV (18h)

Count May Not be

Accurate

W116 X X No Fix

SYSCALL Immediately

after Changing EFLAGS.TF

May Not Behave According

to the New EFLAGS.TF

W117 X X No Fix

IA32_FMASK is Reset

during an INIT

W118 X X No Fix

IO_SMI Indication in

SMRAM State Save Area

May Be Set Incorrectly

W119 X X No Fix

LBR, BTS, BTM May

Report a Wrong Address

when an

Exception/Interrupt

Occurs in 64-bit Mode

W120 X X No Fix

A Thermal Interrupt is Not

Generated when the

Current Temperature is

Invalid

W121 X X No Fix

CMPSB, LODSB, or SCASB

in 64-bit Mode with Count

Greater or Equal to 248

May Terminate Early

W122 X X No Fix

Returning to Real Mode

from SMM with

EFLAGS.VM Set May

Result in Unpredictable

System Behavior

W123 X X No Fix

IRET under Certain

Conditions May Cause an

Unexpected Alignment

Check Exception

W124 X X No Fix

CPL-Qualified BTS May

Report Incorrect Branch-

From Instruction Address