Specification Update

Table Of Contents

Summary Tables of Changes

Specification Update 25

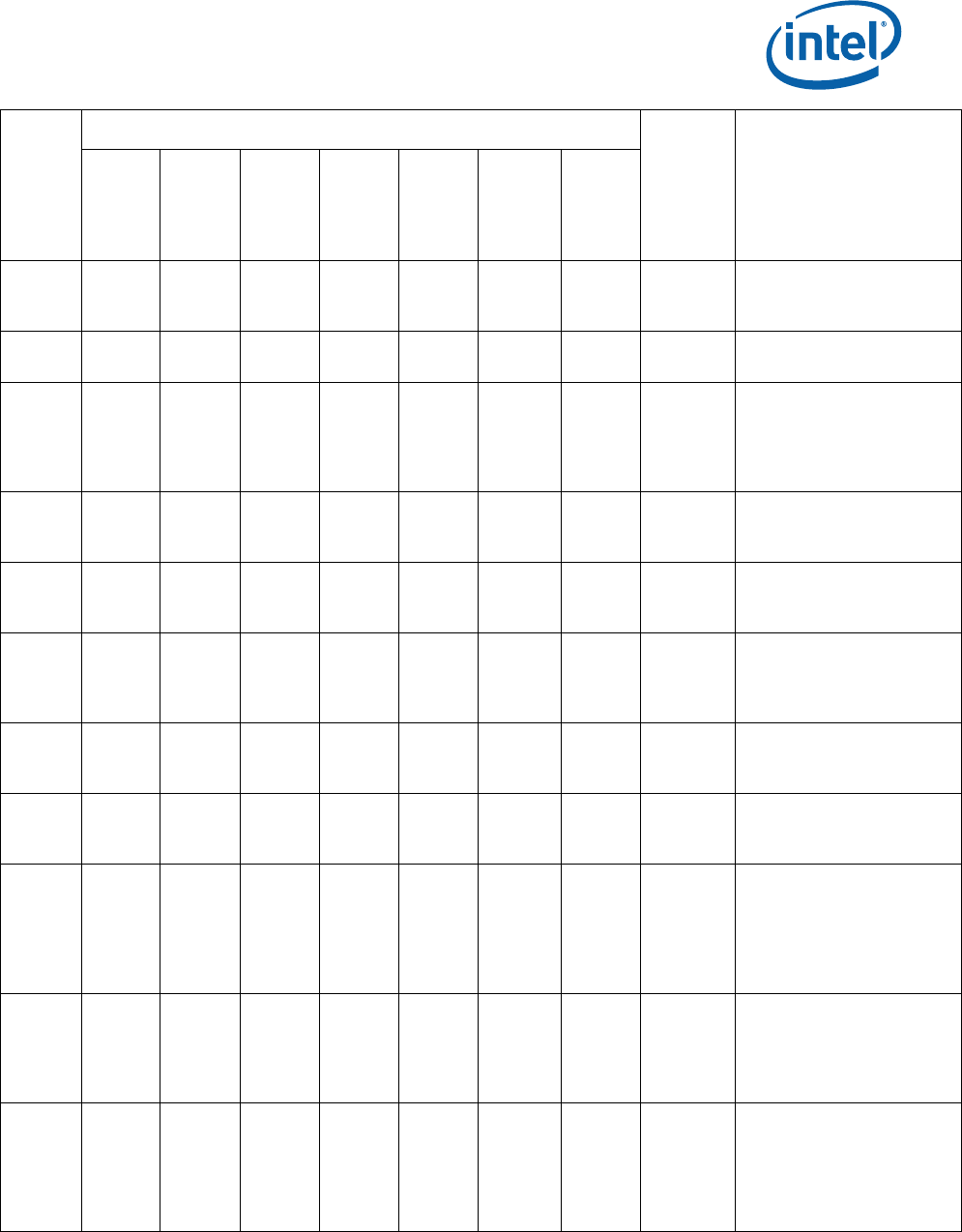

Steppings

NO.

B-1 CPU

Signature

= 06D6h

C-0 CPU

Signature

= 06D8h

B-1 CPU

Signature

= 0695h

C-0 CPU

Signature

= 06E8h

D-0 CPU

Signature

= 06ECh

B-2 CPU

Signature

= 06F6h

A-1 CPU

Signature

= 10661h

Plans

ERRATA

W125 X X No Fix

PEBS Does Not Always

Differentiate Between

CPL-Qualified Events

W126 X X No Fix

PMI May Be Delayed to

Next PEBS Event

W127 X X No Fix

PEBS Buffer Overflow

Status Will Not be

Indicated Unless

IA32_DEBUGCTL[12] is

Set

W128 X X No Fix

An Asynchronous MCE

During a Far Transfer May

Corrupt ESP

W129 X X No Fix

B0-B3 Bits in DR6 May

Not be Properly Cleared

After Code Breakpoint

W130 X X No Fix

REP Store Instructions in

a Specific Situation may

cause the Processor to

Hang

W131 X X No Fix

Performance Monitor SSE

Retired Instructions May

Return Incorrect Values

W132 X X No Fix

Performance Monitoring

Events for L1 and L2 Miss

may Not be Accurate

W133 X No Fix

A MOV Instruction from

CR8 Register with 16-Bit

Operand Size Will Leave

Bits 63:16 of the

Destination Register

Unmodified

W134 X X No Fix

Debug Register May

Contain Incorrect

Information on a MOVSS

or POPSS Instruction

Followed by SYSRET

W135 x x X X Plan Fix

Update of Read/Write

(R/W) or User/Supervisor

(U/S) or Present (P) Bits

without TLB Shootdown

May Cause Unexpected

Processor Behavior