Intel Celeron D Processor 300 Sequence

Table Of Contents

- Contents

- Revision History

- 1 Introduction

- 2 Electrical Specifications

- 2.1 FSB and GTLREF

- 2.2 Power and Ground Lands

- 2.3 Decoupling Guidelines

- 2.4 Voltage Identification

- 2.5 Reserved, Unused, and TESTHI Signals

- 2.6 FSB Signal Groups

- 2.7 GTL+ Asynchronous Signals

- 2.8 Test Access Port (TAP) Connection

- 2.9 FSB Frequency Select Signals (BSEL[2:0])

- 2.10 Absolute Maximum and Minimum Ratings

- 2.11 Processor DC Specifications

- 2.12 VCC Overshoot Specification

- 2.13 GTL+ FSB Specifications

- 3 Package Mechanical Specifications

- 4 Land Listing and Signal Descriptions

- 5 Thermal Specifications and Design Considerations

- 6 Features

- 7 Boxed Processor Specifications

- 8 Debug Tools Specifications

40 Datasheet

Package Mechanical Specifications

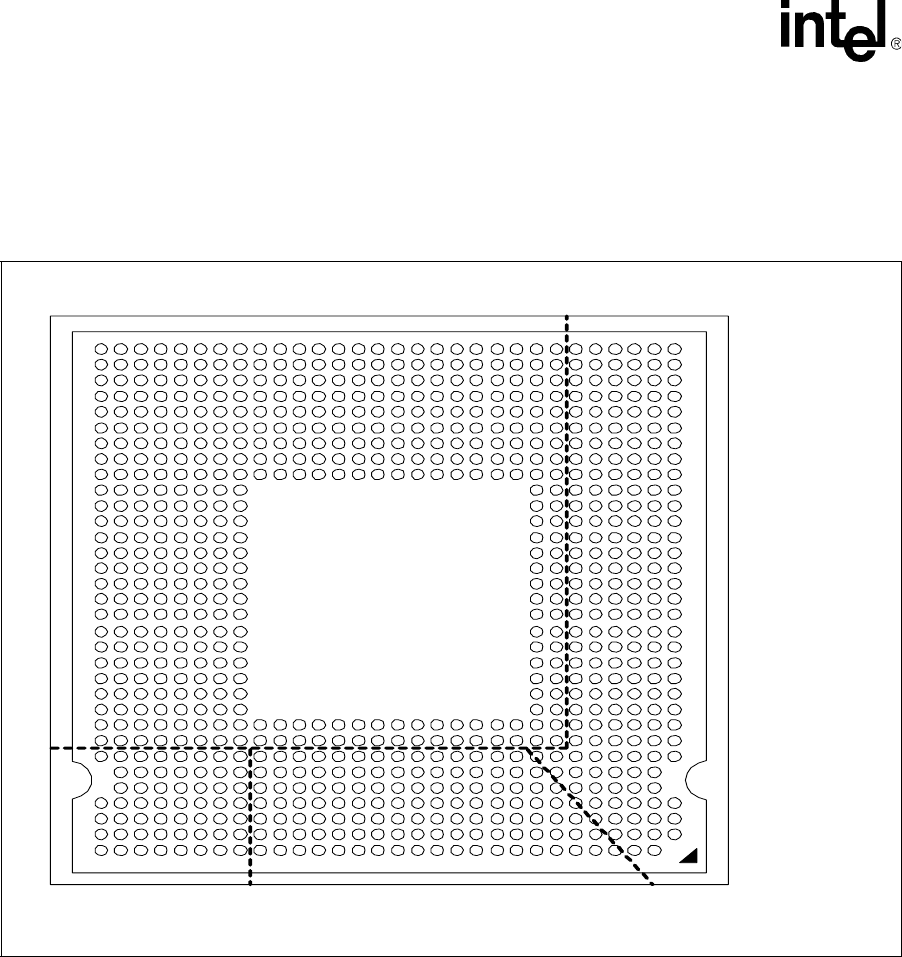

3.9 Processor Land Coordinates

Figure 3-7 shows the top view of the processor land coordinates. The coordinates are referred to

throughout the document to identify processor lands.

.

§

Figure 3-7. Processor Land Coordinates (Top View)

123456789101112131415161718192021222324252627282930

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

AG

AH

AJ

AK

AL

AM

AN

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

AG

AH

AJ

AK

AL

AM

AN

1234567891011121314151617181920212223242526

27282930

775-Land Package Quadrants

(Top View )

V

CC

/ V

SS

V

TT

/ C locks

Data

Address /

Common Clock

/ Async