Intel Celeron D Processor 300 Sequence

Table Of Contents

- Contents

- Revision History

- 1 Introduction

- 2 Electrical Specifications

- 2.1 FSB and GTLREF

- 2.2 Power and Ground Lands

- 2.3 Decoupling Guidelines

- 2.4 Voltage Identification

- 2.5 Reserved, Unused, and TESTHI Signals

- 2.6 FSB Signal Groups

- 2.7 GTL+ Asynchronous Signals

- 2.8 Test Access Port (TAP) Connection

- 2.9 FSB Frequency Select Signals (BSEL[2:0])

- 2.10 Absolute Maximum and Minimum Ratings

- 2.11 Processor DC Specifications

- 2.12 VCC Overshoot Specification

- 2.13 GTL+ FSB Specifications

- 3 Package Mechanical Specifications

- 4 Land Listing and Signal Descriptions

- 5 Thermal Specifications and Design Considerations

- 6 Features

- 7 Boxed Processor Specifications

- 8 Debug Tools Specifications

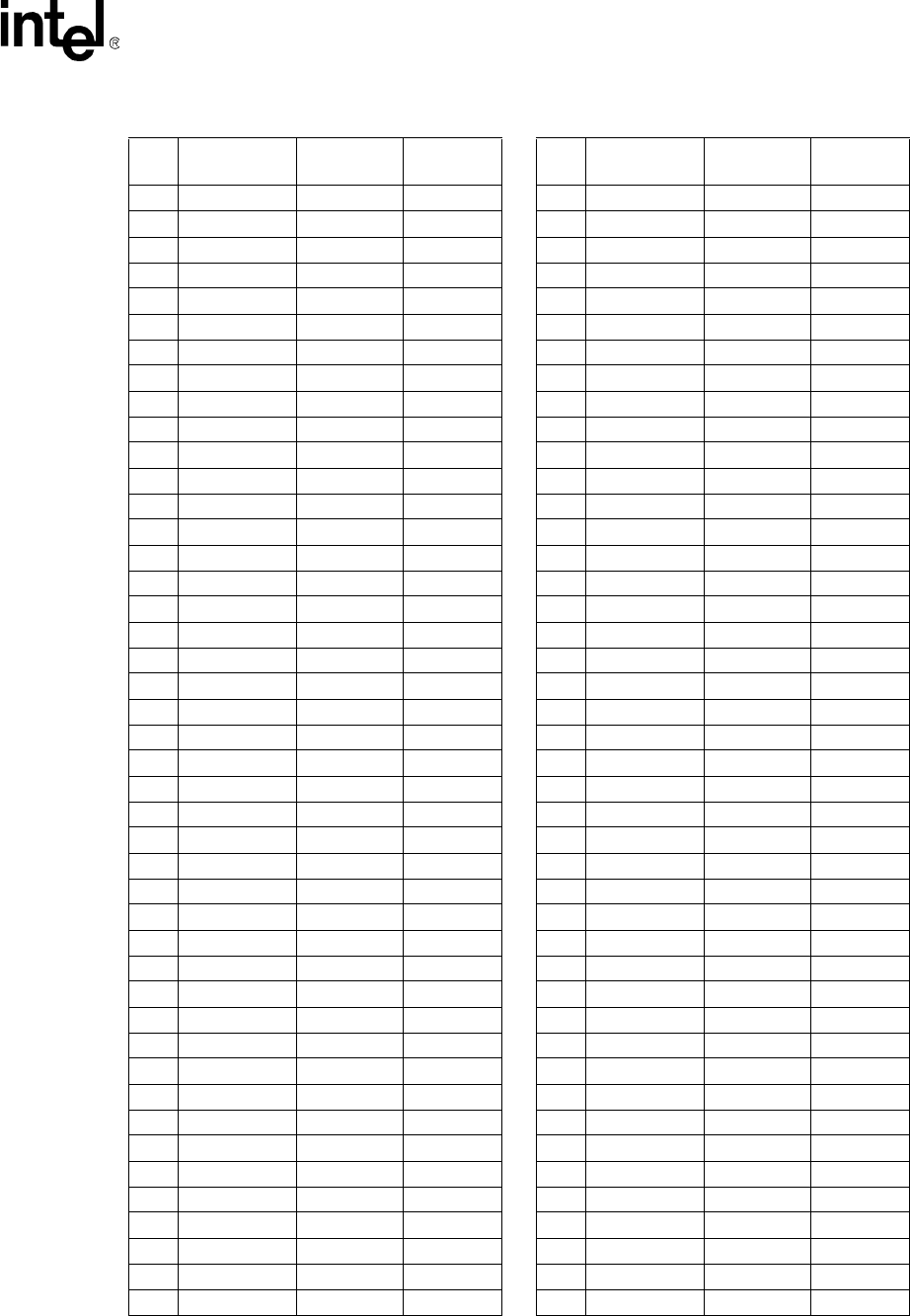

Land Listing and Signal Descriptions

Datasheet 57

R8 VCC Power/Other —

R23 VSS Power/Other —

R24 VSS Power/Other —

R25 VSS Power/Other —

R26 VSS Power/Other —

R27 VSS Power/Other —

R28 VSS Power/Other —

R29 VSS Power/Other —

R30 VSS Power/Other —

T1 COMP1 Power/Other Input

T2 COMP5 Power/Other Input

T3 VSS Power/Other —

T4 A11# Source Synch Input/Output

T5 A9# Source Synch Input/Output

T6 VSS Power/Other —

T7 VSS Power/Other —

T8 VCC Power/Other —

T23 VCC Power/Other —

T24 VCC Power/Other —

T25 VCC Power/Other —

T26 VCC Power/Other —

T27 VCC Power/Other —

T28 VCC Power/Other —

T29 VCC Power/Other —

T30 VCC Power/Other —

U1 VSS Power/Other —

U2 AP0# Common Clock Input/Output

U3 AP1# Common Clock Input/Output

U4 A13# Source Synch Input/Output

U5 A12# Source Synch Input/Output

U6 A10# Source Synch Input/Output

U7 VSS Power/Other —

U8 VCC Power/Other —

U23 VCC Power/Other —

U24 VCC Power/Other —

U25 VCC Power/Other —

U26 VCC Power/Other —

U27 VCC Power/Other —

U28 VCC Power/Other —

U29 VCC Power/Other —

U30 VCC Power/Other —

V1 MS_ID1 Power/Other Output

V2 LL_ID0 Power/Other Output

V3 VSS Power/Other —

Table 4-2. Numerical Land Assignments

Land

#

Land Name

Signal Buffer

Type

Direction

V4 A15# Source Synch Input/Output

V5 A14# Source Synch Input/Output

V6 VSS Power/Other —

V7 VSS Power/Other —

V8 VCC Power/Other —

V23 VSS Power/Other —

V24 VSS Power/Other —

V25 VSS Power/Other —

V26 VSS Power/Other —

V27 VSS Power/Other —

V28 VSS Power/Other —

V29 VSS Power/Other —

V30 VSS Power/Other —

W1 MS_ID0 Power/Other Output

W2 TESTHI12 Power/Other Input

W3 TESTHI1 Power/Other Input

W4 VSS Power/Other —

W5 A16# Source Synch Input/Output

W6 A18# Source Synch Input/Output

W7 VSS Power/Other —

W8 VCC Power/Other —

W23 VCC Power/Other —

W24 VCC Power/Other —

W25 VCC Power/Other —

W26 VCC Power/Other —

W27 VCC Power/Other —

W28 VCC Power/Other —

W29 VCC Power/Other —

W30 VCC Power/Other —

Y1 BOOTSELECT Power/Other Input

Y2 VSS Power/Other —

Y3 RESERVED — —

Y4 A20# Source Synch Input/Output

Y5 VSS Power/Other —

Y6 A19# Source Synch Input/Output

Y7 VSS Power/Other —

Y8 VCC Power/Other —

Y23 VCC Power/Other —

Y24 VCC Power/Other —

Y25 VCC Power/Other —

Y26 VCC Power/Other —

Y27 VCC Power/Other —

Y28 VCC Power/Other —

Y29 VCC Power/Other —

Table 4-2. Numerical Land Assignments

Land

#

Land Name

Signal Buffer

Type

Direction