Intel Celeron D Processor 300 Sequence

Table Of Contents

- Contents

- Revision History

- 1 Introduction

- 2 Electrical Specifications

- 2.1 FSB and GTLREF

- 2.2 Power and Ground Lands

- 2.3 Decoupling Guidelines

- 2.4 Voltage Identification

- 2.5 Reserved, Unused, and TESTHI Signals

- 2.6 FSB Signal Groups

- 2.7 GTL+ Asynchronous Signals

- 2.8 Test Access Port (TAP) Connection

- 2.9 FSB Frequency Select Signals (BSEL[2:0])

- 2.10 Absolute Maximum and Minimum Ratings

- 2.11 Processor DC Specifications

- 2.12 VCC Overshoot Specification

- 2.13 GTL+ FSB Specifications

- 3 Package Mechanical Specifications

- 4 Land Listing and Signal Descriptions

- 5 Thermal Specifications and Design Considerations

- 6 Features

- 7 Boxed Processor Specifications

- 8 Debug Tools Specifications

Datasheet 7

Revision History

§

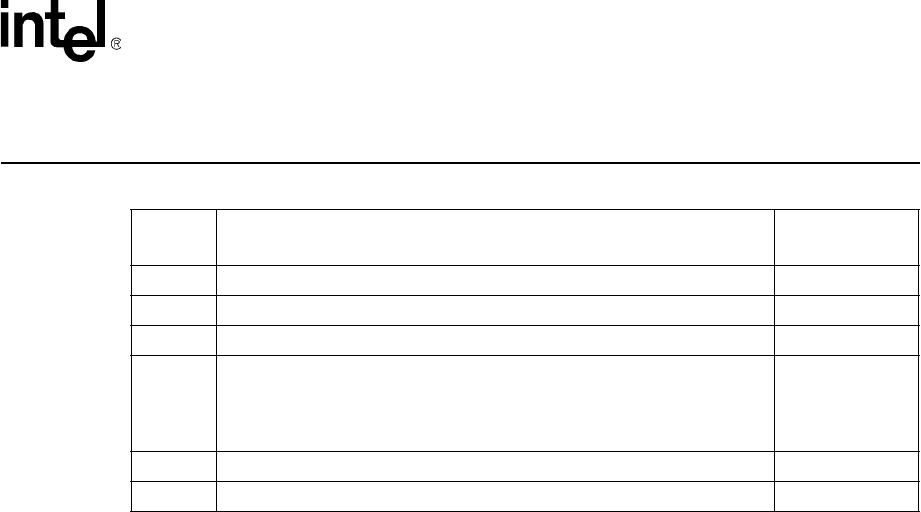

Revision

Number

Description Date

-001 • Initial release September 2004

-002 • Added 3.06 GHz processor November 2004

-003 • Updated Clock Control and Low Power States section in chapter 6 December 2004

-004

• Added support for processor numbers 346, 341, 336, 331, and 326

• Added the letter “J” to processor numbers 345J, 340J, 335J, 330J and

325J

• Added EM64T support

June 2005

-005 • Added support for processor number 351 June 2005

-006 • Added support for processor number 355 December 2005