Intel Celeron D Processor 300 Sequence

Table Of Contents

- Contents

- Revision History

- 1 Introduction

- 2 Electrical Specifications

- 2.1 FSB and GTLREF

- 2.2 Power and Ground Lands

- 2.3 Decoupling Guidelines

- 2.4 Voltage Identification

- 2.5 Reserved, Unused, and TESTHI Signals

- 2.6 FSB Signal Groups

- 2.7 GTL+ Asynchronous Signals

- 2.8 Test Access Port (TAP) Connection

- 2.9 FSB Frequency Select Signals (BSEL[2:0])

- 2.10 Absolute Maximum and Minimum Ratings

- 2.11 Processor DC Specifications

- 2.12 VCC Overshoot Specification

- 2.13 GTL+ FSB Specifications

- 3 Package Mechanical Specifications

- 4 Land Listing and Signal Descriptions

- 5 Thermal Specifications and Design Considerations

- 6 Features

- 7 Boxed Processor Specifications

- 8 Debug Tools Specifications

Datasheet 79

Features

6 Features

This chapter contains power-on configuration options and clock control/low power state

descriptions.

6.1 Power-On Configuration Options

Several configuration options can be configured by hardware. The Celeron D processor in the

775-land package samples the hardware configuration at reset, on the active-to-inactive transition

of RESET#. For specifications on these options, refer to Table 6-1.

The sampled information configures the processor for subsequent operation. These configuration

options cannot be changed except by another reset. All resets reconfigure the processor; for reset

purposes, the processor does not distinguish between a "warm" reset and a "power-on" reset.

6.2 Clock Control and Low Power States

The processor allows the use of AutoHALT and Stop-Grant to reduce power consumption by

stopping the clock to internal sections of the processor, depending on each particular state. See

Figure 6-1 for a visual representation of the processor low power states.

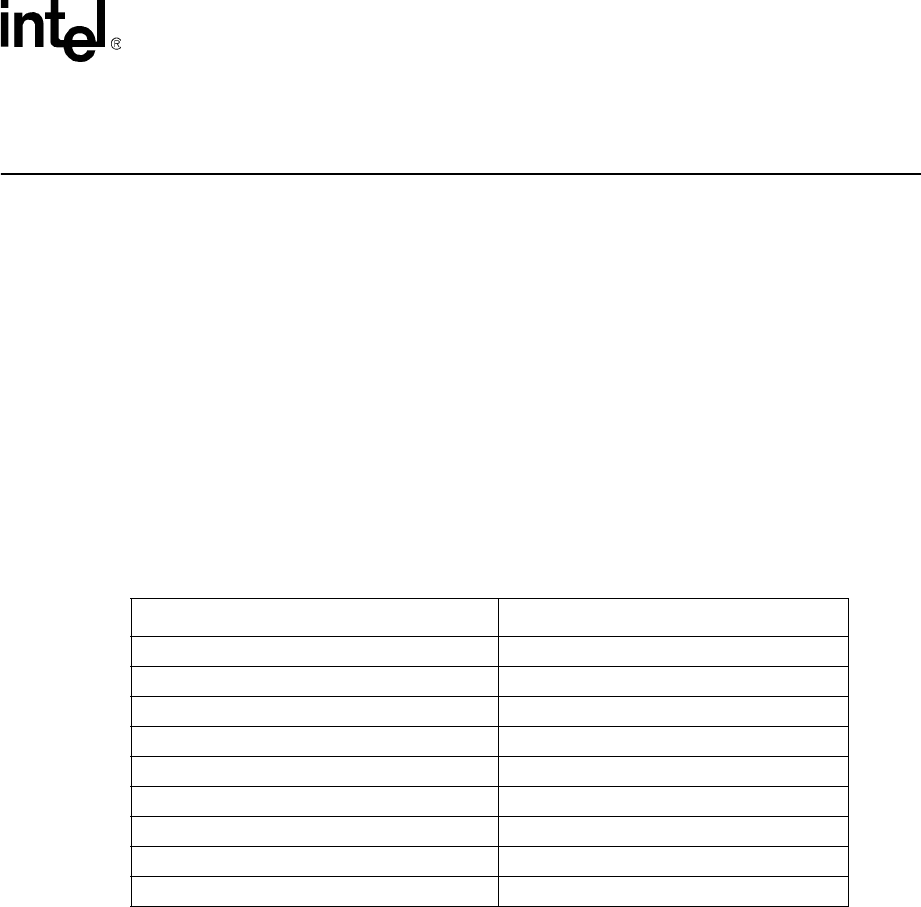

Table 6-1. Power-On Configuration Option Signals

Configuration Option Signal

1, 2

NOTES:

1. Asserting this signal during RESET# will select the corresponding option.

2. Address signals not identified in this table as configuration options should not be asserted during RESET#.

Output tristate SMI#

Execute BIST INIT#

In Order Queue pipelining (set IOQ depth to 1) A7#

Disable MCERR# observation A9#

Disable BINIT# observation A10#

APIC Cluster ID (0-3) A[12:11]#

Disable bus parking A15#

Symmetric agent arbitration ID BR0#

RESERVED A[6:3]#, A8#, A[14:13]#, A[16:30]#, A[32:35]#