Design Guide

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

2

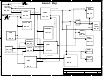

U4B4

V5A_PWRGD

PCI_RST#

MAX809

VR_ON

4

16

VR_SHUTDOWN

GMCH_VCORE_PWRGD

SMC

5

DDR_VR_PWRGD

V1.5_PWRGD

PWR_PWROK

+V3A

U7B1

2

17

PG 43

3

+V5A VR

PG 20

+V12S

3

+V1.5A

19

PG 45

PG 39

18

H_CPURST#

MGM &

VCCP VR

9

PG 39

4

PM_RSMRST#

U6

+V5

PS_ON_SW#

5

5

+V2.5

+V3A

SMC_ONOFF#

PG 29

ICH4

PG 39

PG 6

ON_BOARD_VR_PWRGD

PG 39

MAIN_PWROK

IMVP_PWRGD

H_PWRGD

5

+V1.5S

CPU

PG 32

+V3.3

CK-408

ON_BOARD_VR_ON

5

+V5_ALWAYS

PG 39

PG 3

MAIN2_PWROK

DDR VR

PM_SLP_S4#

+V3.3S

PG 33

8

PG 45

5

Core VR

SMC_RST#

VR_ON

PG 44

POWER

5

10

PM_PWRBTN#

PG 41

PM_PWROK

U4B5

+VDC

PG 19

10

6

SMC_PROG_RST#

Power On Sequence

U7A5

-V12S

VR_PWRGD_CK408#

11

GMCH

18

PM_SLP_S3#

PG 39

1

PG 7

5

DC/DC

U7A3

12

DELAYED_VR_PWRGD

+V1.25S

PG 39

PG 21

RST_HDR

+V5S

7

INTERPOSER_PRES#

U4B3

U4B3

U4B3

U4B3

13

14

15

OFF_BOARD_VR_PWRGD

INTERPOSER_PRES

PG 39

PG 39

4.401

Power On Check list

A

47 50Monday, September 15, 2003

Intel 855GM/GME CRB

<Doc>

Title

Size Document Number Rev

Date: Sheet

of

Project: