Intel Celeron Processor Specification Update

INTEL

®

CELERON® PROCESSOR SPECIFICATION UPDATE

15

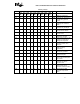

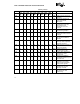

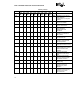

Summary of Errata

NO. CPUID/Stepping Plans ERRATA

650h

A0

651h

A1

660h

A0

665h

B0

683h

B0

686h

C0

68Ah

D0

6B1h

A1

6B4h

B1

C40 X X X X Fixed Incorrect chunk ordering may

prevent execution of the

machine check exception

handler after BINIT#

C41 X X X X X Fixed UC write may be reordered

around a cacheable write

C42 X X X X X X Fixed Resume Flag may not be

cleared after debug

exception

C43 X X X X Fixed Internal cache protocol

violation may cause system

hang

C44 X X X X X X X X X NoFix GP# fault on WRMSR to

ROB_CR_BKUPTMPDR6

C45 X X X X X Fixed Machine Check Exception

may occur due to improper

line eviction in the IFU

C46 X X X X X X X X X NoFix Lower bits of SMRAM

SMBASE register cannot be

written with an ITP

C47 X X X X X X Fixed Task switch may cause

wrong PTE and PDE access

bit to be set

C48 X X X X X X X X X NoFix Cross-modifying code

operations on a jump

instruction may cause a

general protection fault

C49 X X X X X X X Fixed Deadlock may occur due to

illegal-instruction/page-miss

combination

C50 X X X X X X X X X NoFix FLUSH# assertion following

STPCLK# may prevent CPU

clocks from stopping

C51 X X X X X X Fixed Floating-point exception

condition may be deferred

C52 X X X X X X X Fixed Cache Line Reads May

Result in Eviction of Invalid

Data