Intel Celeron Processor Specification Update

INTEL

®

CELERON® PROCESSOR SPECIFICATION UPDATE

16

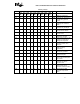

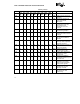

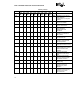

Summary of Errata

NO. CPUID/Stepping Plans ERRATA

650h

A0

651h

A1

660h

A0

665h

B0

683h

B0

686h

C0

68Ah

D0

6B1h

A1

6B4h

B1

C53 X X X X X NoFix FLUSH# servicing delayed

while waiting for

STARTUP_IPI in 2-way MP

systems

C54 X X X X X NoFix Double ECC error on read

may result in BINIT#

C55 X X X X X NoFix MCE due to L2 parity error

gives L1 MCACOD.LL

C56 X X X X X NoFix EFLAGS discrepancy on a

page fault after a

multiprocessor TLB

shootdown

C57 X X X X X NoFix Mixed cacheability of lock

variables is problematic in

MP systems

C58 X X X X X NoFix INT 1 with DR7.GD set does

not clear DR7.GD

C59 X X X X X NoFix Potential loss of data

coherency during MP data

ownership transfer

C60 X X X X X NoFix Misaligned Locked access to

APIC space results in a hang

C61 X X X X X NoFix Memory ordering based

synchronization may cause a

livelock condition in MP

Systems

C62 X X X X X NoFix Processor may assert

DRDY# on a write with no

data

C63 X Fixed Machine check exception

may occur due to improper

line eviction in the IFU

C65 X X NoFix Snoop request may cause

DBSY# hang

C66 X Fixed MASKMOVQ instruction

interaction with string

operation may cause

deadlock

C67 X X X X X NoFix MOVD, CVTSI2SS, or

PINSRW Following Zeroing

Instruction Can Cause

Incorrect Result