Intel Pentium 4 Processor on 90 nm Process

Table Of Contents

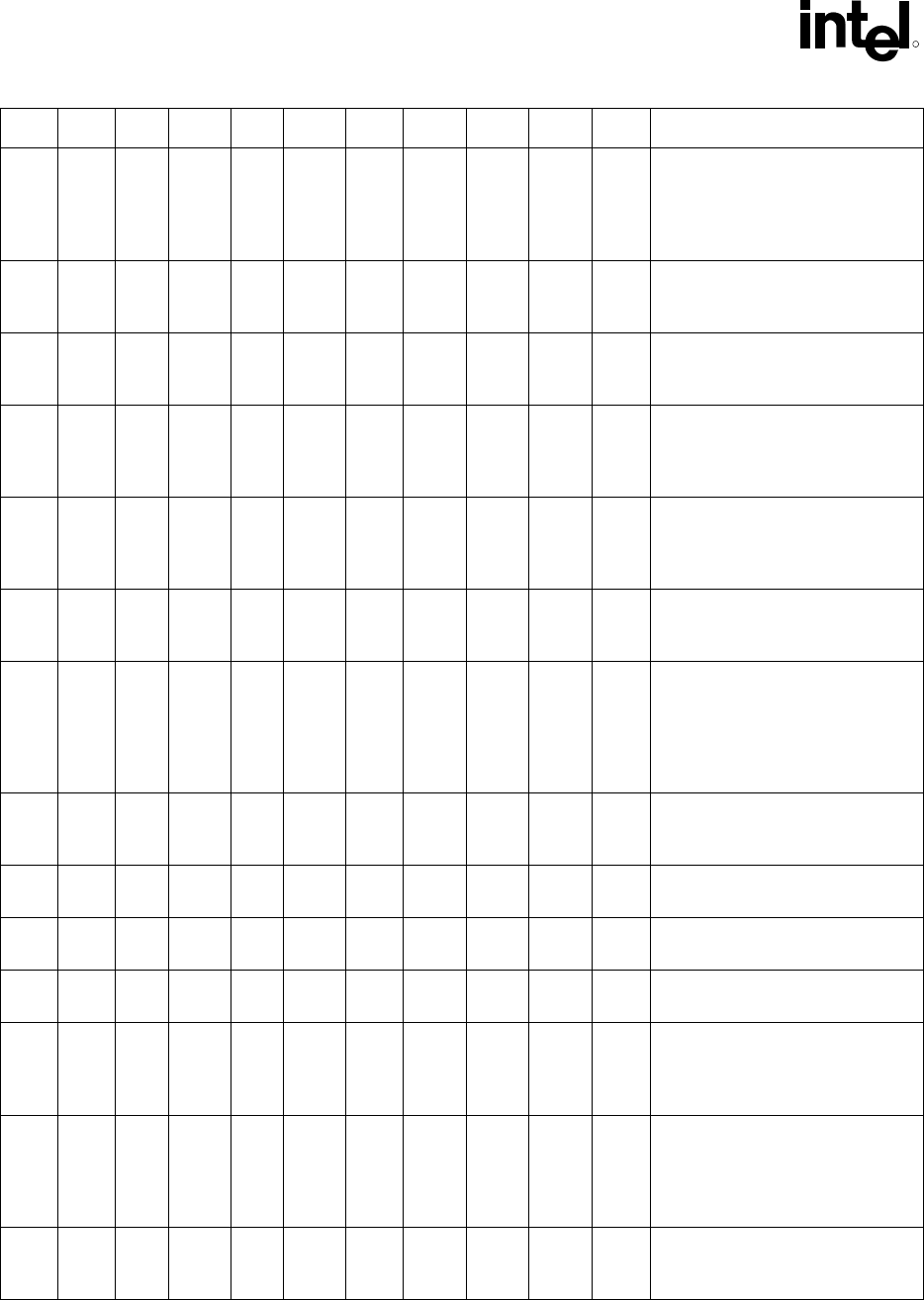

Summary Tables of Changes

R

10 Intel

®

Pentium

®

4 Processor on 90 nm Process Specification Update

NO. C0

1

D0 LD0

2

E0 LE0

2

G1

1

LG1

2

LN0

2

LR0

2

Plan ERRATA

R10 X X X X X X X X X

No

Fix

The Processor Signals Page-Fault

Exception (#PF) Instead of

Alignment Check Exception (#AC)

on an Unlocked CMPXCHG8B

Instruction

R11 X X X X X X X X X

No

Fix

FSW May Not Be Completely

Restored after Page Fault on

FRSTOR or FLDENV Instructions

R12 X X X X X X X X X

No

Fix

Processor Issues Inconsistent

Transaction Size Attributes for

Locked Operation

R13 X X X X X X X X X

No

Fix

When the Processor Is in the

System Management Mode (SMM),

Debug Registers May Be Fully

Writeable

R14 X X X X X X X X X

No

Fix

Shutdown and IERR# May Result

Due to a Machine Check Exception

on a Hyper-Threading Technology

Enabled Processor

R15 X X X X X X X X X

No

Fix

Processor May Hang under Certain

Frequencies and 12.5% STPCLK#

Duty Cycle

R16 X X X X X X X X X

No

Fix

System May Hang if a Fatal Cache

Error Causes Bus Write Line (BWL)

Transaction to Occur to the Same

Cache Line Address as an

Outstanding Bus Read Line (BRL)

or Bus Read-Invalidate Line (BRIL}

R17 X X X X X X X X X

No

Fix

A Write to an APIC Registers

Sometimes May Appear to Have

Not Occurred

R18 X Fixed

Some Front Side Bus I/O

Specifications are not Met

R19 X X X X X X X X X

No

Fix

Parity Error in the L1 Cache May

Cause the Processor to Hang

R20 X Fixed

BPM4# Signal Not Being Asserted

According to Specification

R21 X X X X X Fixed

Sequence of Locked Operations

Can Cause Two Threads to

Receive Stale Data and Cause

Application Hang

R22 X X X Fixed

A 16-bit Address Wrap Resulting

from a Near Branch (Jump or Call)

May Cause an Incorrect Address to

be Reported to the #GP Exception

Handler

R23 X X X X X X X X X

No

Fix

Bus Locks and SMC Detection May

Cause the Processor to Hang

Temporarily