Intel Pentium 4 Processor on 90 nm Process

Table Of Contents

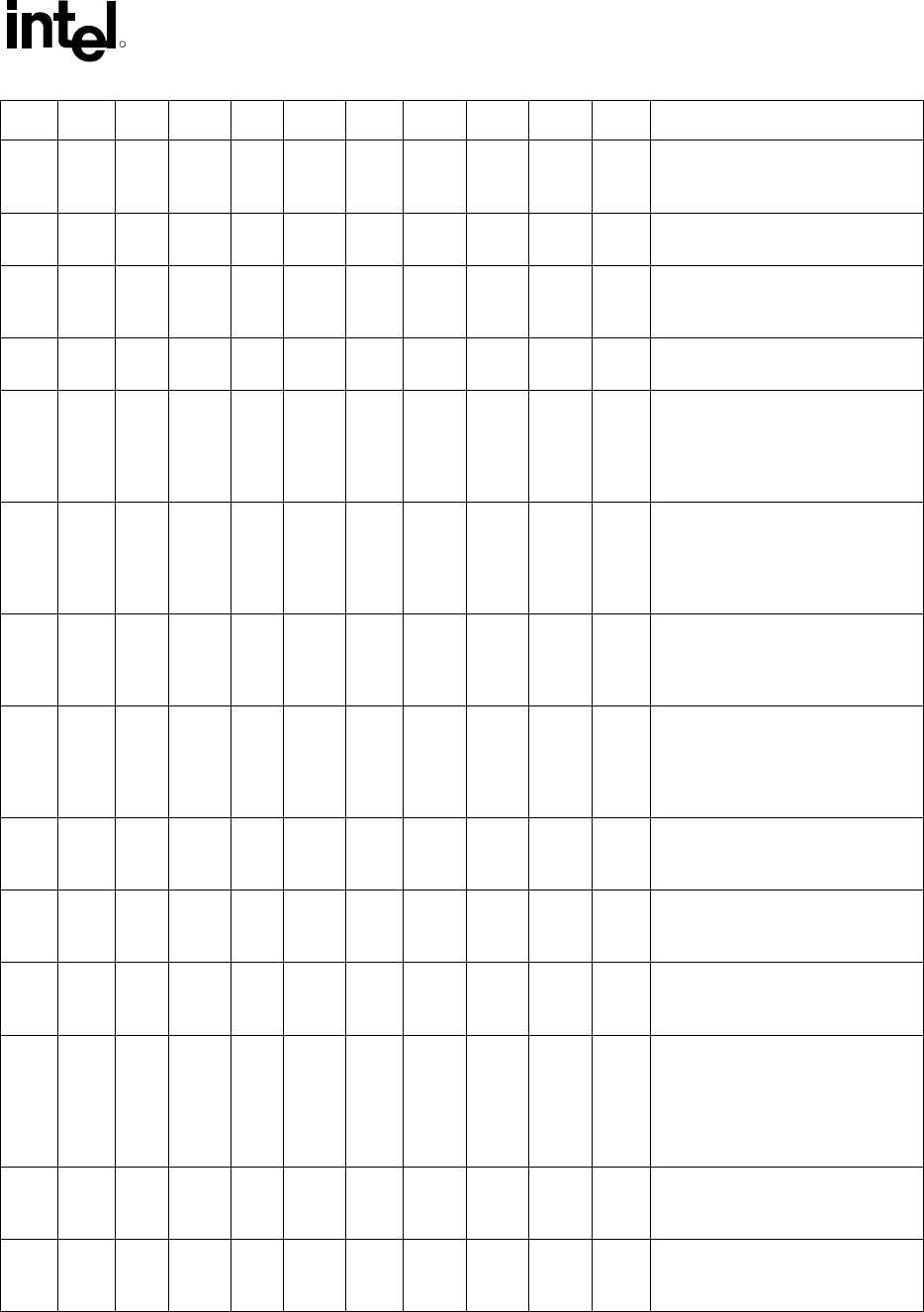

Summary Tables of Changes

R

Intel

®

Pentium

®

4 Processor on 90 nm Process Specification Update 11

NO. C0

1

D0 LD0

2

E0 LE0

2

G1

1

LG1

2

LN0

2

LR0

2

Plan ERRATA

R24 X Fixed

PWRGOOD and TAP Signals

Maximum Input Hysteresis Higher

Than Specified

R25 X X X Fixed

Incorrect Physical Address Size

Returned by CPUID Instruction

R26 X X X X X X X X X

No

Fix

Incorrect Debug Exception (#DB)

May Occur When a Data Breakpoint

is set on an FP Instruction

R27 X X X X X X X X X

No

Fix

xAPIC May Not Report Some Illegal

Vector Errors

R28 X X X X X Fixed

Enabling No-Eviction Mode (NEM)

May Prevent the Operation of the

Second Logical Processor in a

Hyper-Threading Technology

Enabled Processor

R29 X X X X X X X X X

No

Fix

Incorrect Duty Cycle is Chosen

when On-Demand Clock

Modulation is Enabled in a

Processor Supporting Hyper-

Threading Technology

R30 X X X X X X X X X

No

Fix

Memory Aliasing of Pages as

Uncacheable Memory Type and

Write Back (WB) May Hang the

System

R31 X X X X X X X X X

No

Fix

Interactions Between the Instruction

Translation Lookaside Buffer (ITLB)

and the Instruction Streaming Buffer

May Cause Unpredictable Software

Behavior

R32 X Fixed

STPCLK# Signal Assertion under

Certain Conditions May Cause a

System Hang

R33 X Fixed

Missing Stop Grant

Acknowledge Special Bus Cycle

May Cause a System Hang

R34 X Fixed

Changes to CR3 Register do not

Fence Pending Instruction Page

Walks

R35 X Fixed

Simultaneous Page Faults at

Similar Page Offsets on Both

Logical Processors of a Hyper-

Threading Technology Enabled

Processor May Cause Application

Failure

R36 X Fixed

The State of the Resume Flag (RF

Flag) in a Task-State Segment

(TSS) May be Incorrect

R37 X X X X X X X X X

No

Fix

Using STPCLK# and Executing

Code From Very Slow Memory

Could Lead to a System Hang