Intel Pentium 4 Processor on 90 nm Process

Table Of Contents

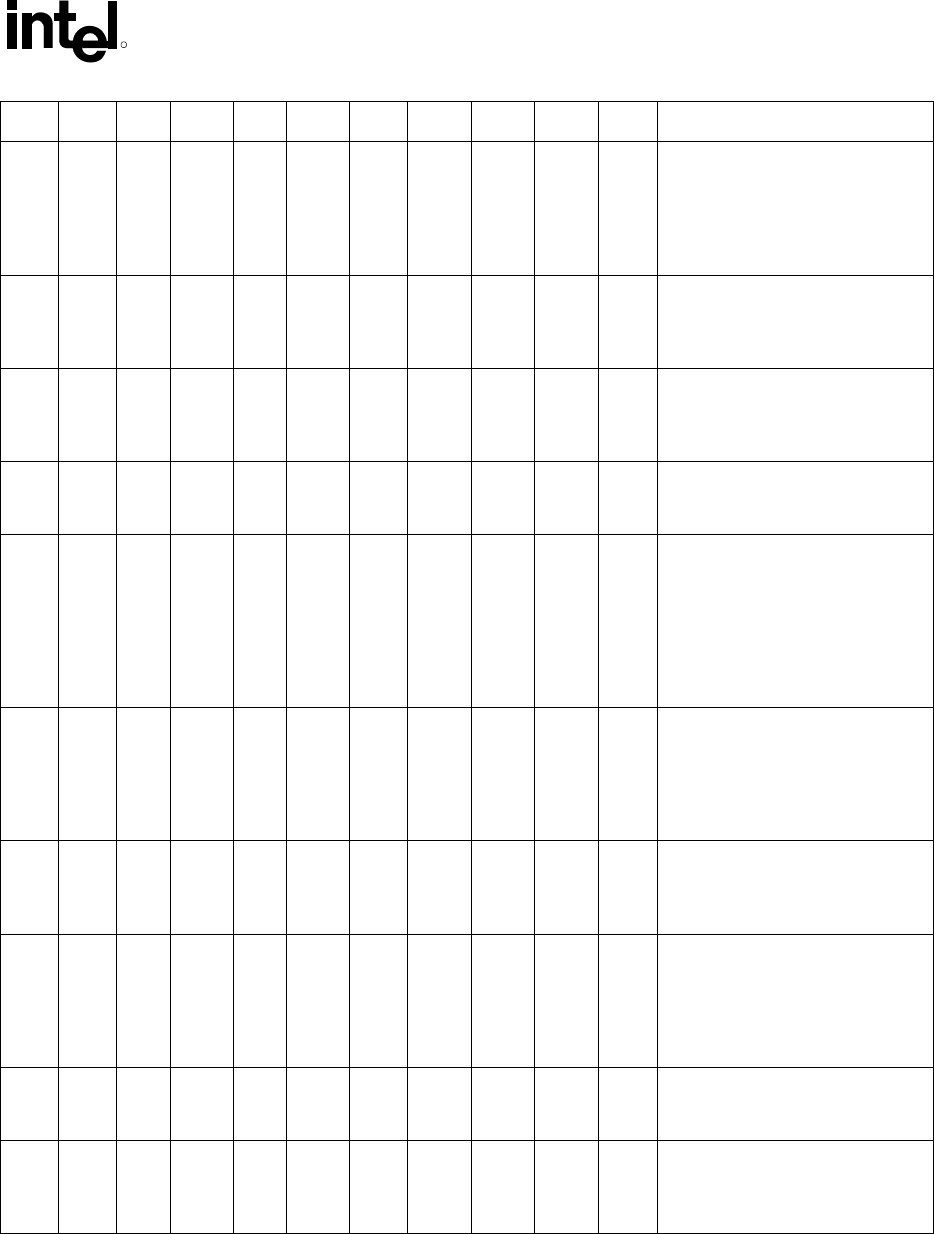

Summary Tables of Changes

R

Intel

®

Pentium

®

4 Processor on 90 nm Process Specification Update 15

NO. C0

1

D0 LD0

2

E0 LE0

2

G1

1

LG1

2

LN0

2

LR0

2

Plan ERRATA

R77 X X X X X X X X X

No

Fix

Memory Ordering Failure May

Occur with Snoop Filtering Third

Party Agents after Issuing and

Completing a BWIL (Bus Write

Invalidate Line) or BLW (Bus

Locked Write) Transaction

R78 X X X X X X X X X

No

Fix

Control Register 2 (CR2) Can be

Updated during a REP

MOVS/STOS Instruction with Fast

Strings Enabled

R79 X X X X Fixed

TPR (Task Priority Register)

Updates during Voltage Transitions

of Power Management Events May

Cause a System Hang

R80 X X X X X

No

Fix

REP STOS/MOVS Instructions with

RCX >=2^32 May Cause a System

Hang

R81 X X X X Fixed

An REP MOVS or an REP STOS

Instruction with RCX >= 2^32 May

Fail to Execute to Completion or

May Write to Incorrect Memory

Locations on Processors

Supporting Intel® Extended

Memory 64 Technology (Intel®

EM64T)

R82 X X X X Fixed

An REP LODSB or an REP LODSD

or an REP LODSQ Instruction with

RCX >= 2^32 May Cause a System

Hang on Processors Supporting

Intel® Extended Memory 64

Technology (Intel® EM64T)

R83 X X X X

No

Fix

A Data Access which Spans Both

the Canonical and the Non-

Canonical Address Space May

Hang the System

R84 X X X X X X X X Fixed

Running in SMM (System

Management Mode) And L1 Data

Cache Adaptive Mode May Cause

Unexpected System Behavior when

SMRAM is Mapped to Cacheable

Memory

R85 X Fixed

CPUID Instruction Incorrectly

Reports CMPXCH16B as

Supported

R86 X X X X X Fixed

Unaligned PDPTR (Page-Directory-

Pointer) Base with 32-bit Mode PAE

(Page Address Extension) Paging

May Cause Processor to Hang